读the art of electronics(电子学)书中,遇到的一些具体疑问,求助。

时间:10-02

整理:3721RD

点击:

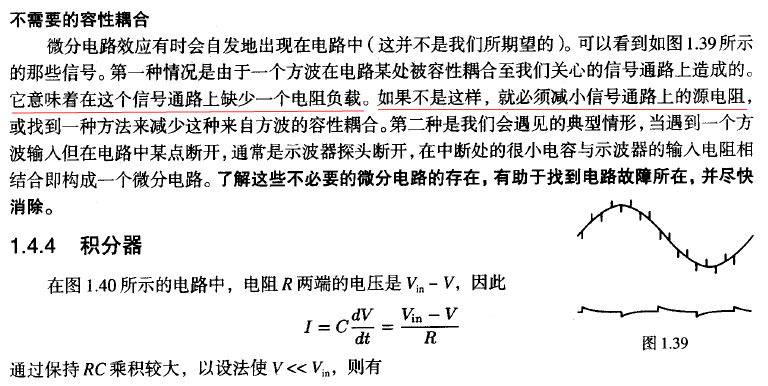

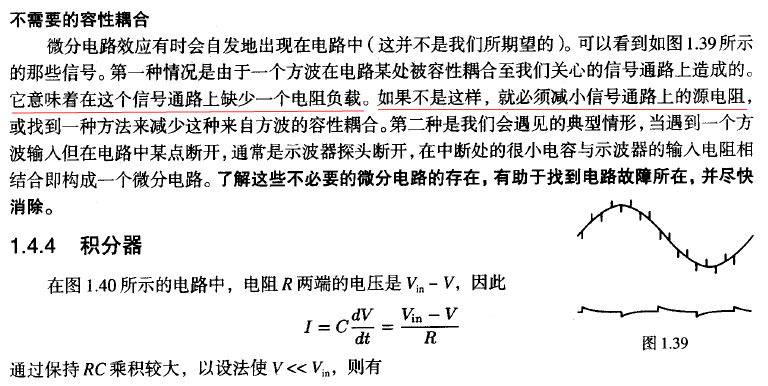

《the art of electronics》中文版P22页中的一段话,如下附图所示,其中红色标识的这两句话没理解,为什么意味着“信号通路上缺少一个电阻负载,”“或必须减小信号通路上的源电阻”?请教各位!

干扰通道的C和信号通道上的有效负载构成了一个RC微分电路。如果有个跳变信号在干扰源上,信号通道的负载就相当于微分电路R上的波形。减小RC时间常数就可以减小加到负载上的有效干扰信号。要么减小C(与干扰源屏蔽或者远离),要么减小信号通路上的有效负载(减小源电阻,或者减小负载电阻)。通常CMOS电路的输入是高阻的,增加一个负载电阻可以减小信号通路上的输入阻抗。

sun_ic,谢谢先。明白了一些!

你所说的“减小RC时间常数就可以减小加到负载上的有效干扰信号”具体指什么。

减少RC常数,实际是使充放电时间更短,充放电的波形更窄,应该并不减少干扰信号的幅度。怎么理解你所说的这句话呢?

“增加一个负载电阻可以减小信号通路上的输入阻抗”,这里对于高阻输入的cmos电路,“增加”具体应该是并联一个负载电阻吧,不知我理解对否?

感觉只是用RC的微分模型还不足以描述干扰的真正影响。如果只是抽象出RC模型的话,在时域上分析,干扰通道上的时间常数的减少,可以减少实际干扰的有效“能量”-- 即减少持续时间。理论上讲peak值减少不了。但由于器件的输入还有信号通路也有容性。可以简单的在频域直观的分析一下:如果负载电阻是无限大,则是一个电容的分压电路。不管什么频率的干扰都会加在输入端。加上一个负载电阻,相当于把一个“高通”滤波器的截止频率推向高端。这样“低频”的干扰就被削减了。当然实际的模型比这复杂。只要定性的看出趋势就可了。

作为负载是并联在输入的高阻上。

多谢,