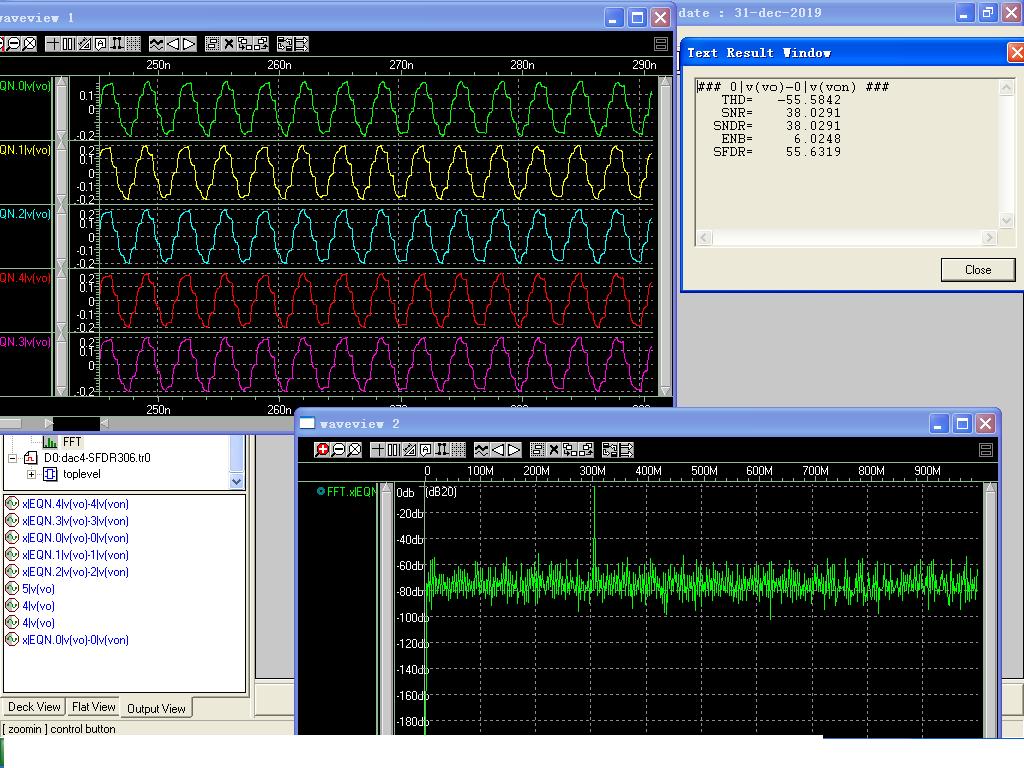

高速DAC SFDR

补充一句 从频谱上来看 SFDR 并没有那么高的,怎么显示的结果不对呢?

because dac needs a filter to filter out frequency at sample frequency.

your waveform is not so bad --> no glitches, no periodic distortions

so SFDR is good

可能是你DA本身的过,我推荐给你一颗高速DAC,性能如下:

。4:1 Multiplexing for Each Input Bit of DAC

。Double Sampling Rate (DSR) DAC with Analog Output Sampling

。Rate Twice of Clock Rate

。12-bit, > 8-Gsps DAC Output

。12-bit resolution DAC with Double Data Rate (DDR) Latches

• DAC analog output has sampling rate twice of clock input rate

• Complementary analog outputs with 50-Ω back terminations

• Complementary divided-by-2 and divide-by-4 clock LVDS outputs for data

synchronization

• Divide-by-2 and Divide-by-4 clock output drivers with enable/disable control

without interrupting internal operations of the chip

• On-chip 100 ohm termination between each differential LVDS input data and

RESET pair

• 3.5 W power consumption

• TQFP package with Exposed Pad to enhance grounding and heat dissipation

。Full Spectrum SFDR SFDR 60 dBc

恩 高速很难做啊

频谱看上去很漂亮啊

已经很不错了

学习学习,

ddddddddddddddd