求助:数字锁相环

时间:10-02

整理:3721RD

点击:

请问各位大虾:

1、数字锁相环的输入时钟是一个还是两个?

2、数字锁相环的输出时钟可以比参考时钟的性能更好吗?如果是,是什么性能提高了?

3、输出时钟和参考时钟在鉴相器进行比较,请问频率可不可以不一样,就是说一个是另一个的整数倍,每几个时钟周期比较一次。

小弟急等,先谢一声!

1、数字锁相环的输入时钟是一个还是两个?

2、数字锁相环的输出时钟可以比参考时钟的性能更好吗?如果是,是什么性能提高了?

3、输出时钟和参考时钟在鉴相器进行比较,请问频率可不可以不一样,就是说一个是另一个的整数倍,每几个时钟周期比较一次。

小弟急等,先谢一声!

求助:数字锁相环

1.一般而言,输入时钟是一个。但另外还有一个本地时钟,且频率要高得多,与输入时钟无需倍数关系。

2.可以。锁相环有低通特性,较高频率的噪声(或称为抖动)可以被降低。

3.可以不一样。每几个周期比较一次并不难实现。

求助:数字锁相环

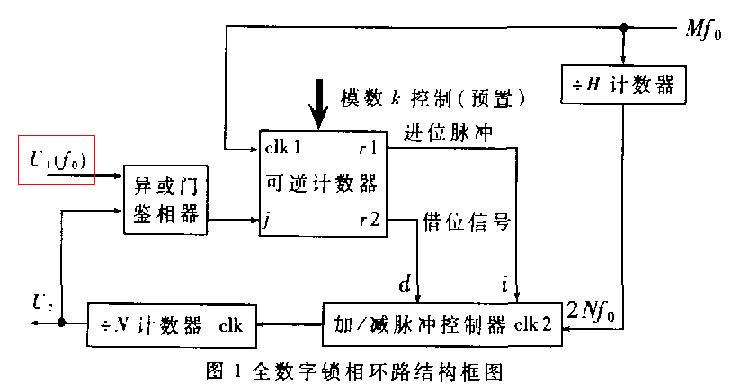

楼上的大侠,本地时钟是不是在鉴相器和输出时钟比较的那个(图中做红色标记的)?它是个内部时钟吧,其精度是很高的,这样理解对不对?

求助:数字锁相环

红色标记的U1(f0)是输入时钟,输出时钟的频率和相位以它为基准来调整。所以对这个时钟的频率精度要求较高。(它频率偏了,则输出时钟频率也跟着偏)

我所说的本地时钟是指Mf0。它的频率精度无需很高,不过它的频率高(不是精度高)对环路特性的控制有好处,对输出时钟的抖动特性也有好处。

求助:数字锁相环

多谢大侠指点!

呵呵,同谢

xiexiele !

学习了!