通电时供电电压会瞬间降低可能是什么问题

用H型桥电路控制两个背靠背的LED发光

PMOS作开关,Vccs限流

两个LED间隔5ms交替发光,发光pulse为0.2ms

问题现象:

开通(开始发光)的瞬间,供电电压会急剧下降,只有1us长,形成向下的peaks,通路上其它点的信号会产生相应的向上或向下的peaks,这瞬间电流(2A)远超过允许范围(600mA),但之后的0,2ms里又回复正常了。不知道这些peaks会对电路产生哪些损害,至少信号是不好的,可能是什么原因呢?

另外一个关于供电电压滤波的问题,如果用了过大的电容,会有哪些副作用?

还有,由OPA和NMOS加电阻组成的VCCS,具体工作过程,是不是先差分放大,然后再根据Id和Vgs的关系控制电流呢,这样的话,要使NMOS工作在线性区,OPA选择上要注意什么呢?

以上,谢谢指点啦~菜鸟啊菜鸟,没经验啊没经验

版块太火,之么快就沉了。

你的H桥驱动电路有没有加死区,现像来看应该是死区没有作好。

两侧的PMOS控制开关,间隔5ms交替导通,即各自周期为10ms,而导通时间又各自只有0.2ms,是不会同时导通的啊。但是NMOS是加OPA组成VCCS,起控制电流作用,设计是想在灯灭的区间做调节,所以有半个周期导通,半个周期关断,现在一侧是这样的,另一侧有问题,一直导通,电路是对称的,也闹不明白为什么不一样。一直导通这边,在另一侧导通时,会分流;半周期导通那边,只在本身导通时有值,但都在pulse上升沿有瞬间的大peak。

把电路贴出来分析如何?光看文字描述靠想象力琢磨是挺累的事。

看不清那4根控制线是怎么处理的?

控制信号来自单片机

分别经过NMOS3/4传给PMOS1/2

经过OPA传给NMOS1/2

电路似乎有点问题,要关死NMOS好像不容易。不知为何要让OPA376的负输入端接在1Ω上,这样当NMOS关闭时1Ω的压降也为0,超过了单电源供电的OPA376的共模输入范围,应该给个定值才对,比如单片机电源的Vcc/2。

OPA+NMOS是作VCCS用,正常工作的话,Id=Vin+/1Ω,也就是Vin+ = Vin-。现在是Vin+信号半周期高半周期低,相应地,output半周期满偏半周期为0,即NMOS在它工作的半个周期里导通,且同时起限流作用,在另一侧工作的半周里关断。对VCCS的结构属于照猫画虎,所以我也想知道在选择OPA和NMOS时应该注意什么,在网上查说这个部分是线性的,那么是不是意味着,NMOS应该工作在线性区,OPA的输出也应该是在一个范围内可变的呢?那一般的OPA就不行了吧。

在源极串电阻限流,FET会进入放大区发热,这个办法须统筹考虑器件的功耗,因图上电源电压看不清,也不知负载电阻有多大,所以不好判断。

也可直接把限流电阻串在负载上,这样半导体都处于开关状态,其实才600mA末级驱动用三极管就行了,控制电路也简单,觉得这里的两个运放挺大材小用的。

电源是3.7V电池,充满电时4.2V,负载电阻不一定,因为Sensor是可换的,但新的Sensor是考虑最高600mA来设计的。下面用VCCS,主要是不光要限流,还要根据功能调节,运放入端是DAC给的信号。谢谢提示,也许要连着控制带电路一块改,我想先弄清开关上升沿的peaks是哪来的。一般说瞬间共同导通,产生短路,增大功耗,电压会降下来,也会烧坏器件。现在也许是1us太短,还不致于烧坏,但是交替开关的间隔那么久,哪里会产生共同导通哩?

几乎可以肯定,OPA376负输入端接1Ω电阻是最大的疑点,当NMOS截止时OPA负输入端也趋于0,而正输入是受控端,被完全驱动到地电位并使运放输出反转是不容易的,瞬间短路很可能就是由它产生。

为了验证这点,建议将OPA的负输入端改接到由电阻分压产生的Vcc/2处试试。

谢谢。

这个部分是控制电流用的,接Vcc/2,就没用了。看来要改电阻,或者大改。

确实有输出翻转的困难,电路是对称的,但一边能翻下来,另一边完全不行,这和负输入端驱动到0的关系具体是怎样呢?能稍微多讲点吗,谢谢啦~

另外,查了一些电流源电路,大多提到为恒流源,把开关的作用整合进去,除了延时,会不会出现其它恶劣的效果?

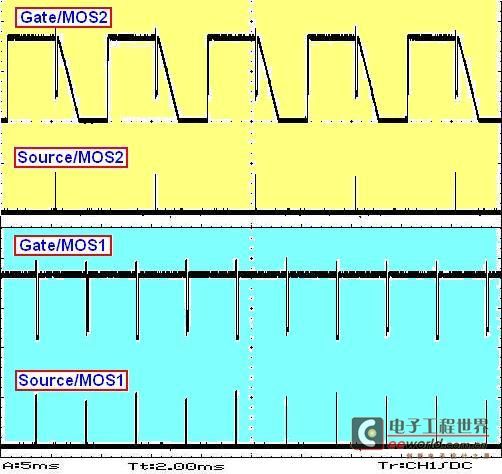

比较这两组电路的情况,也可以看出,Source极的peaks只出现在MOS管导通的情况下,说明另一侧开关导通时,在LED点亮前,先从这里瞬间短路了。那也不对,不通过LED,哪来的电流呢。

不知两张图的CH1和CH2分别测的是电路里的哪四个点?驱动运放和MOS3、4的是怎样的电路?

MOS3,4是受单片机信号控制的,这部分的信号都符合预期,PMOS的工作也正常。

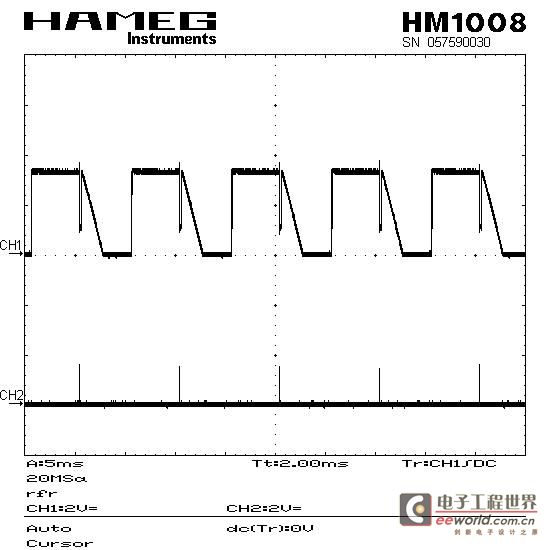

第一张图的CH1和CH2是右上角MOS2的G和S,因为应该断开的时候G降到0了,所以MOS2没有对另一侧电路造成短路,S信号就是如愿的10ms周期。

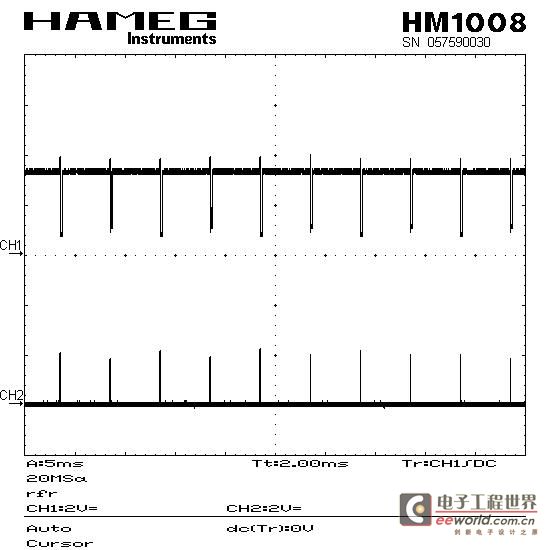

第二张图的CH1和CH2是左下角MOS1的G和S,因为G没降下来,MOS1始终导通,在另一侧电路通电时,就会造成短路及分流,S信号的周期中间就出现了计划外的电流。这里最奇怪就是G没有翻下来,电路是对称的,难道是layout的影响?对了G信号下降较少的pulse是应该导通工作时,下降较多的pulse是另一侧应该工作时。

至于应该导通时,为什么有瞬间大电流,就只能出在LED上了,查到别人的经验说,可能是并联的电容不够,或者可以再并一个电阻,帮它放电,下一次充电时也许效果就会好,但这样就得放很大很大的电阻才不会影响LED们正常工作吧。

了解opa现在的工作过程以后,有个疑问,输出在满偏和0之间切换,工作在非线性区,还能以虚短虚断来分析吗?那么这个VCCS的功能也就不能保证了吧。应该换opa使其工作在线性区?

1、先按你所说的把波形图整理附上,有清晰、统一的基础方好深入讨论。

2、按说FET的G和S是同相的,怎么图上是反相的?是不是你说的“S”实际是“D”?

3、假如先不管运放和FET的状态,从单片机出来的一共有几个独立的信号?本身的时序对不对?为什么G是细脉冲而不是接近50%占空比的方波?

能否把电路再贴全一些,尤其是从单片机引脚出来的那部分,以及设想的驱动时序示意图?

另,为使分析简单化,建议暂去掉负载处的电容,只接纯电阻假负载看波形。