这个脚为什么这样接的?不是说一般悬空的么?

时间:10-02

整理:3721RD

点击:

这个1脚为什么这样接的?不是说一般悬空的么?

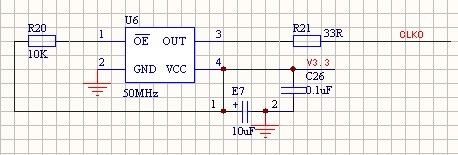

U6 是一个有源晶体振荡器 1脚是使能脚(low active)

如果是使能脚 怎么通过电阻接到了电源上? 明明标的是低电平使能

应该是画错

但是晶振的1脚不是一般都悬空的么?

你要看是什么晶振 这种不是普通的晶振 , 这种是有源晶振

哦 那是什么晶振啊 有什么特别的地方? 是给FPGA用的

1脚不使能的话, 是没有50MHz的频率输出的 这种晶振内部有振荡电路

我是说这个跟普通的晶振有什么特别的地方?就多一个使能脚么?

可以独立工作

是啊 本来就有源晶振啊

普通晶振是谐振器 需要搭配主芯片里面的振荡电路工作

我是说 这个有使能脚的晶振 跟1脚一般悬空的有源晶振 有什么不同 工作上 就是多个使能而已?

是的

哦 那电阻的大小是怎么定的? 10K

起到待机消耗电流小的作用 这个就是一个简单的数量电路的 高低电平的问题, 你不怕待机电流大 你选择1K 或者更小的都可以啊

大致是明白了 就是不知道有没有内部电路 那可以知道这个怎么减小电流了

VCC通过10K电阻把电平拉低到/OE,此时电流很小

学习