丢人的设计失误

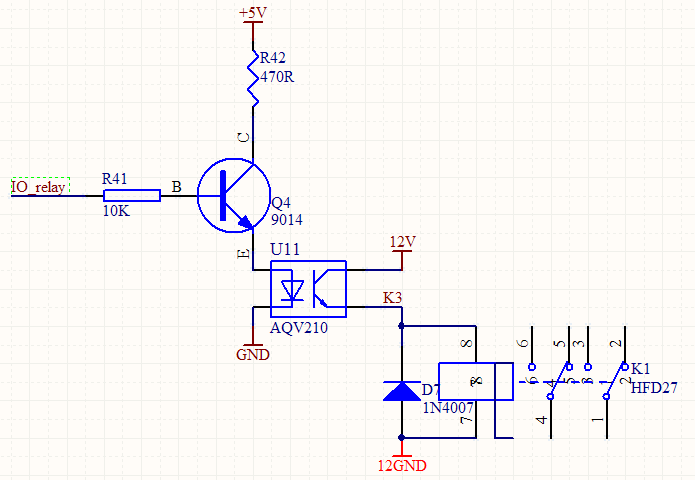

光耦 直接驱动 继电器?

应该 有电流放大级。。。

光耦没有那么大的驱动电流吧?

射随接法,驱动光耦的电压不够。

要把三极管换成批恩皮管,E、C倒过来。

光耦驱动 12v继电器 没有加限流电阻吧

这样一导通 直接将12v电源拉到地了

疑问:光耦的左端发光部分可不可以用灌电流加个限流电阻?

射极一直有输出电压,不受控制。

IO口不能控制三及管导通的。

三及管的E点应该接地

光藕应该串接到5V和三极管的C及上去。

你的电路设计的很有创意!

呵呵 什么意思呢

驱动光耦,电流足够就可以了吧

射级的输出电压能让光耦导通吗?

只要单片机能承受的了相应的灌电流大小就可以

为什么要加限流电阻呢,那样会由于分压的关系可能导致继电器线圈达不到吸合电压而无法吸合

期待高手优化,修正

来算下够不够吧。

1、不知继电器的吸合电流是多少,姑且算20mA吧。

2、光耦PC817D的最小电流传输比CTR=300%(?)

3、由此可知驱动光耦的电流应≧20/3≒6.7mA

4、Ie=6.7mA在470Ω上的压降≒3.15V。

5、查手册光耦LED的正向压降VF≦1.4V。

6、上述两者叠加得三极管射极电位Ve应≧4.55V。

7、三极管基极电位Vb=Ve+0.7V=5.25V。

8、还有基极串联电阻R41上压降……

—— 已经超过电源电压了,还能驱动得了吗?

当然,实际的器件参数可能没那么差,但设计就一定要以最坏的情况计算,才能保证万无一失。

计算很多,看起来 有道理。。。。。。。。。光耦 输出 可以是 模拟量?继电器 是否稳定?

限流电阻太大了 三极管工作在放大区 不是饱和区 此时不是开关作用了

楼上有一点说对了,三极管没饱和。但这样的射随接法是不会饱和的,把电流加大到烧管子也不会。

这个是我最终改进的电路图,大家看看还有什么问题啊。控制三极管的IO口最大输出20MA,继电器线圈额定功率一个为580MW,另外一个为2W。

实际在使用上面电路图的时候,光继电器210在继电器线圈功率为2W的时候输出的压降偏大,达到2.2V,这样分给继电器线圈的电压就只有12-2.2=9.8V了,继电器的最低吸合电压为9V,在目前的测试中还没有出现问题,但是有隐患。

应该接成共射级放大电路的形式?

晕,你怎么还不明白,

再说一次:

三及官的E端接地。

把光藕(含电阻)移动到三极管的C及上去,也就是说,

电阻的一个脚接5V,光藕的脚接三及官C及。

你做的不是饱和电路。而是放大电路。

你的Vbe是变化的,

必须固定E点电位,B点作为控制输入才有意义。

你画的第二个图虽然好一点,但还是有隐患。从设计的角度,根本不合格的。

你把K换做光藕就是了。

第一张图和第二张图用的光耦没有比较性??

这样的接法不就是共射级放大电路吗,放大倍数为Hfe本身,呵呵

以上我上传的两个电路都存在两个问题,一个是输入驱动光耦的问题,另外一个是输出驱动继电器的问题。

何必啊,继电器本身就隔离了,还要光藕干什么,浪费成本,一个三极管直接控制就得了 。

19楼的电路可以用,但为防上电瞬间继电器误动作,建议:

1、三极管基极对地跨接一个22kΩ电阻;

2、把基极限流电阻R41减小至12kΩ。

正常的话不可能有那么大的压降,建议查一下AQV210有没接得不合适,因为这个光偶是6脚,图中未反映出来,是可以用于AC的,如果拿AC开关用于DC,会增加一个二极管的正向压降。

一般而言,把负载串在射极做开关电路是不合适的,但这个电路有它的特殊性,光耦负载是二极管不是电阻,19楼电路里的E点电位并不会随电流无限上升,不会高过1.5V,所以三极管还是可以饱和的。从另一个角度看,由于使三极管ON的控制阈值不是通常的0.7V,而变成了2V左右,电路的抗干扰性被提高,反倒变成了好事。

啊 不好意思啊 那个PHOTOMOS型号应该是AQY210,4个脚的

为了抗干扰,呵呵...........

菜鸟 来冲冲电 学习一下

这个防误动作的是好方法,正好改改,呵呵

谢谢呀

光藕会冒烟的

为什么呢?