求教一个模拟电路的简单问题

我无法正常设置其静态工作点。根据资料显示当IB为10uV左右,并且VCE在8V左右的时候,IC应该是4MA多吧,为什么跟仿真结果不一致呢?

本人新手。请问下大家是哪里出了问题呢?

怎么没人回呀?自己顶下

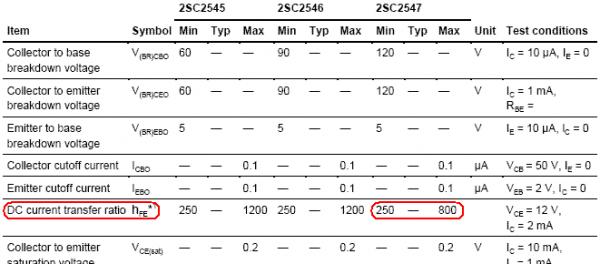

楼上贴的只是该器件的典型曲线,并非每个管子都如此,三极管参数的离散型是很大的。 曲线上当 Ic=8mA 时hFE大约为700,但器件手册写了hFE可以在250~800范围内,想必仿真库用的是hFE的最小值吧。

谢谢!你还查过资料了啊。但是这个型号的在这个工作点应该差别不这么大吧,而且我很难调处来合适的放大电路,是我自己的原因吗?

查资料还不容易吗?拿型号撒狗一搜就啥都给叼来了。你现在的 Ic/Ib=2860/10.5≒272,差不多就是手册里hFE的最小值,所以不能说结果不对。

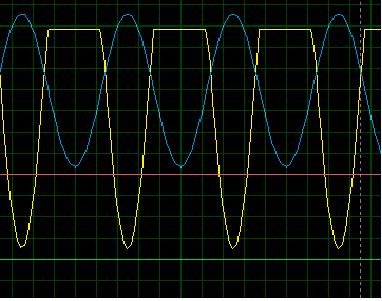

非常感谢你,可是这个三极管总是调不好,电压输出的正半周期被削平,是截止失真吗?可是为什么改变静态工作点或者减小输入振幅都无济于事呢?还请大侠指教!

楼主这个电路具体要实现什么功能呢

建议你把看到的波形贴出来瞅瞅。在理想的静态工作点上,当出现截顶失真时,上下两边的波形都应差不多同时开始截顶。

恩,没有问题

这是波形,怎么调都会失真。蓝色原波形

这是静态工作点,比原先那个好点

1、作为交流放大器,输入点是哪里?怎么没见隔直电容?

2、输入、输出信号的电压幅值分别是多少?(请标一下坐标)

3、红、绿色是什么线?

我也想这样问,LZ要把问题的上下文描述清楚,我们才好帮忙啊!

没有数据没法分析

1。有隔直电容的,只是没有在图中。用PROTEUS仿真的,用的正弦信号源。

2.好的,我再上个图片。

3.用PROTEUS仿真的四输入示波器,那两个是另外两个输入。

上图是仿真全图,因为我感觉这个三极管需要的工作点较高所以加的直流电压很高。

输入的是18V的正弦交流信号

莫非将18V交流不串隔直电容直接加在基极上?那负半周时咋办?三极管肯定就截止削顶了。

非常感谢这位大哥,我是一个新手,还在上大二,数字和单片机学的还行,模拟刚开始。可以问下你QQ号是多少吗?以后也许还有很多向你请教的地方。

扫瑞,我没有上QQ的条件。

给放大器的输入应该是在一个偏置(静态工作点)基础上叠加交流信号,交流信号源通过一个隔直电容接到R1、R2连接处就能达到这个效果。

输入18V可能太大,输出会呈现上下削顶的波形(而不是像现在的单边削顶),碰到这种情况减小输入信号的振幅就行了。

LZ 能不能把你的仿真文件也放上来,不然有很多细节无法知道。

恩,受教了,呵呵。

1,因为示波器是交流耦合,所以你看黄线好像只有10.5格,就是说只有55V。其实它的最低点已经是120V+了,再叠加55V,它的顶点已经是180V,电源一共就180V,所以当然削顶了。你把A通道设为直流耦合,然后再把分辨率从5V调到20V,你就能看到确切的波形了。

2,Vout=Vdd-Ic*Rc=Vdd-Ie*Rc=Vdd-(Ve/Re)*Rc=Vdd-(Vb-0.6)*(Rc/Re) (不考虑发射极输出电阻,因为一般只有几十,相比Re几K来说很小)

所以,Vb增加,Vout是减少的,Vb减少,Vout增加。这是一个反相放大器,放大倍率约为Rc/Re。

3,假设晶体管能完全导通,就是说Vce=0,那么Rc和Re也要对Vdd分压。所以发射极电压不可能太高,进一步,基极电压也不能太高,基极偏置(也是分压)也就不能乱偏置。

4,基极合理偏置后,静态Vb确定,静态Vout也就确定。然后就要叠加交流成分上去。首先,交流输入摆幅不能太大,使得Vb小于0。其次,结合2,3,Vout和Ve都有限制。如果超出范围,就会被削平。

5,基极耦合电容存在与否,电路响应是不一样的。因为它起到隔离作用的同时,也引入了相移。输入电压有可能还在上升,基极却已经在下降了,导致输出也开始上升了。

学习一下