mosfet irf3205 并联不均流

电路中没有短接,查过。 我怀疑是并联不均流引起的。

有高人遇到过这种情况吗?如何解决。谢谢!

如果并联电路没接错,那么你有新定律发表了。

用万用表量一下,确认是不是电流分配不均匀的问题,因为导通时等效的电阻很小,只要各支路的阻抗差一点,上面的电流就是几倍的关系。

当时想的是很好的,没想到会这样,郁闷

好的,我试试,有结果我会及时反馈。谢谢回答!

并联凭啥会均流呢?

还有“横流区域”是啥?

并联的时候有一个电流分配的问题,谁的多谁的少的问题。

恒流区,是这个词。

MOSFET参数的均一性没那么好,要定量控制“恒流”怕是不太容易吧,把电路图亮出来讨论如何?

其实说起来很简单,只不过很少有人这么用而已。mosfet用在恒流区,猫兄可以看看他的pdf,没记错的话实在前几页,有个曲线,电流在那个区域基本恒定,我就是通过控制gs的电压来控制id的电流的。恒流可以做到,毋庸置疑。

IRF3205是75A大容量管子,PDF上的那些图画的也是100A上下的曲线,而且只是典型参数,没有数值保证,想要在开环情况下控制到3A谈何容易?除非另接有反馈电路。如果有反馈电路,那么不是一句话能说得清楚的,不看着图就没法讨论了。

再说,既然IRF3205有≧75A的连续电流容量,何必还要均摊这区区3安培?莫非说的不是这个型号?

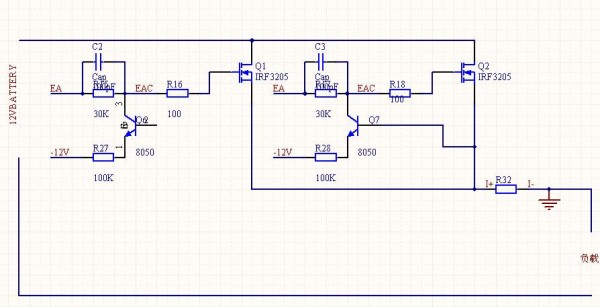

我这里面有一个pi,我用的pdf是alldatasheet的irf3205资料。贴个图上来,篇幅有限,这是2个并联的图。四个的结构和2个的一样,再加两个就ok。

前面提到的问题是这么出现的,33k那个电阻,我误焊为8。3k了,所以就出现那个问题了。我换过来以后,除了基本上各个管子的温度差不多了。

但是当整个电路流过8A时,每个管子2A,发热很大,我测了一下,GS电压3.4V,ds电压10V,发热量很大,按你说的不应该这么热的啊。

像你说的一样,确实4.5v以下没有数据支持。

10V×8A=80W=一只大功率白炽灯泡,确实会滚烫。

只有一部分电路,看不清咋分配电流的,也不清楚负载要求的是电压源还是电流源。

何不考虑用一只管子做PWM降压,如需电流源则另用一只管子控制电流,这样不会发烫。

10v没错,但是8A是4个分配的,一个2A左右,20w也够呛啊。

我这玩意就是给电池放电用的(12v电池要求恒流放电),所以电源就是实验的时候模拟一块电池。降压斩波考虑过,那会有断流的现象,我是为了恒流才选这个方案的。这么控制发热应该是在所难免的了,关键是怎么散热了。

ea就是一个控制信号,让管子工作在横流区域。电流分配那个事儿我估计发热量都差不多,就应该算是平均了吧!微小差异总会有的。我这次布板子的时候已经很对称了。这个话题可以告一段落了。

谢谢猫兄支持。

看见楼主在11楼给出的图和数据后,问题就清楚了:

半导体器件参数的离散性(不一致性)是设计中必须考虑的,多只管子并接,当然谁的内阻小,谁也就“贡献”大(电流大),就最热(V2/R),如果再工作在极限状态,那么最终第一个被烧坏的可能也就是它。

其实这种并联运用是很普遍的,通常的工程解决方法有两点:第一是个笨办法:删选,尽可能使用参数一致的管子(很难的);第二就是搞些折衷---加接均衡电阻,就是每只管子都要串接一个(经过计算的)适当的电阻;同理,在使用多只管子串接时,就要接并联的均衡电阻了。

如果都不行(或不允许),可能就要考虑加强散热等的工艺手段,或者更换管型了。

您说的这种办法我也考虑过,但是我要做的每只管子的电流有2A,而且是工作在恒流区,ds电压限定了,在6v左右(也就是后端负载和管子分压)这样一个管子上的功耗就很大,如果加限流电阻,要求功率就得很高,如果加零点几个欧姆的达不到限流作用(但是这时候电阻的功率就要求8W左右)如果加大一点儿的,1---2欧姆的,I^2*R算一算很大,好像很难买到满足要求的电阻,而且是在印刷电路板上。更难。我现在考虑的1、找一下大功率三极管看能不能有更好的解决办法2、加散热系统,我现在这个小盒子散热片肯定是不行了,1分钟的时候盒子烫手,更不可能长时间为电池放电了。

感谢纯净的硅的真诚回答!

又想了想,一件事情不是很明白,我错把8.3k焊成33k,为什么会引起分流不均呢! 换句话说,g端的电阻对分流有多大影响?

xiaoxif先生说的两种方案都是工程上很实用的,就是要:均衡。

这里的主要矛盾已不是恒不恒流的问题,关键在于如何均分总电流,由于器件的离散型,开环控制G肯定没戏。这样的控制器只做一台调巴调巴或许能凑合,做1000台上流水线咋办?

多谢!呵呵~

问题在于,FET的漏极电流跟门-源电压(或LZ说的G端电阻)之间的关系没有定量的制约式可用,那些图表都只是些定性的东西。

楼主说可以终止这个讨论了(见在15楼的回复),可我觉得没有真正完结这个讨论,想法如下:

1、如果这是个电池放电器的设计,可能会存在一个设计基本思路的问题;

2、此前并没有得到一些关键性的参数,例如电池的恒流放电的电流和终止放电的参考电压(虽然在这里不重要);电路图上很重要的一个电阻(实际上是放电回路的DUMMY--假负载)的阻值,等等;如此终止,岂非让大家成了摸象的盲人?

3、图纸不全,好多关键的被省略掉了,例如,按现在的电路图,那只三极管形同虚设(因为它始终是饱和导通的,)这也是电阻(33k,图上是30k)焊错了导致偏压变化的原因,等等。

笔者以为,这里有许多值得探索的内容,包括设计基本考虑的和具体电路的,等等。就此终止,实在有点遗憾和扫兴?

因此如果可能,希望给出准确的图纸,继续讨论。

两个具体问题:

1、楼主问:“又想了想,一件事情不是很明白,我错把8.3k焊成33k,为什么会引起分流不均呢!换句话说,g端的电阻对分流有多大影响?“

你给的电路图中,没有出现这个阻值,按上下文的关系,估计是和电容并联的那个30k电阻。如上,那只三极管的E通过100k电阻接到-12V,而B连接的电压最低为0,因此这个管子始终是导通,而且是饱和导通的,这就形成了有33(8.3)K电阻和100k电阻分压的FET-G的偏压电路,改成8.3k以后,达到加强FET-G的偏置,通过控制电流,达到降低FET-DS间的等效电阻,可能会得到Pd下降的结果。(因为电路不全这里是趋势性的判断)。g 端的电阻对分流有多大的影响?本质而言不是电阻,而是电阻变化对偏压的影响。对管子的控制全指着这个电压的。

2、望能修改图纸中的负载、电源画法,这样的示意图画法完全可理解为电池+-->电池- -->负载-->地(当然不是这么连接的)

。

我非常理解仙猫先生几次希望见到图的要求,原因很简单:”图纸是工程师的语言“。

通过三位的讨论我学到很多,谢谢

有道理,我觉得如果每一路都加上一个限流电阻,可能会有所帮助

确实是这样的。

1、我做这个东西的初衷就是做一个恒流放电装置,实验室自己用。没打算投产,主要是为了测定电池参数。

2、我今天又做了一些实验,其实就是mosfet和负载在进行分压,如果mosfet上分压大,mosfet就会发热大,正确调节负载电阻(我用一个30A可变电阻器)可以缓解发热的问题。

对于两个具体问题

1、很感谢你的耐心解答,我能理解你的意思。谢谢。确实是我的疏忽,造成了不该有的问题,30k那是图上的标记,手头只有33k就用了。

2、对于图的画法,确实有待改进。由于要采样,所以控制地和负载的地不共地。

至于图纸,我能理解两位的苦衷。能为我解决到这个程度已经感到万分感激了!

图纸实在不方便公开敬请谅解,但是大概思路可以分享。

将采集到的电流通过一次放大,另外还有电流的给定,有电位器调节,然后进行pi调节,最终将信号控制EA,完成整个过程。

斑竹谦虚了

前面没注意是恒流的线性区,如果饱和考虑的就是Rdson,如果线性区就是等效电阻

就是电子元器件的分散性,这个问题普遍存在

每个MOS的热阻严格意义上并不完全相等

随着温度的上升,器件参数是变化的,特别是等效的电阻

是因为你的MOS管控制和管子本身特性差异的问题,因为在MOS放大区很窄,控制电压相同而D脚电压不同,要是做得是 横流建议用三极管控制比较好些,否则就是驱动电压不够导致MOS管道通不充分