一个峰值保持电路工作原理求助

时间:10-02

整理:3721RD

点击:

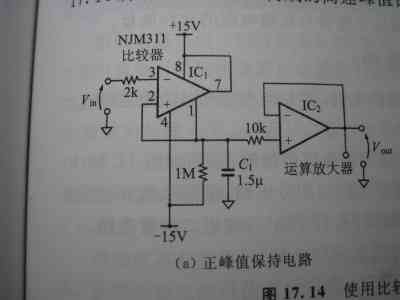

我在做一个检测装置时,由于需要对被检测的电压波形进行峰值保持,在查阅一些资料后,我从《运算放大器应用电路设计》(马场清太郎著)一书中看到附件中的正峰值保持电路,但我对它的工作原理不太明白,因此希望高手能讲解一下它是怎么工作的。其中对于它将输出直接接在电源上特别疑惑。

还有一个问题是,电容的充电时间和保持时间问题。如果在附件中的峰值保持电路中,电容的充电时间应该怎么估算,保持时间又该怎么估算呢?

不甚感谢。

还有一个问题是,电容的充电时间和保持时间问题。如果在附件中的峰值保持电路中,电容的充电时间应该怎么估算,保持时间又该怎么估算呢?

不甚感谢。

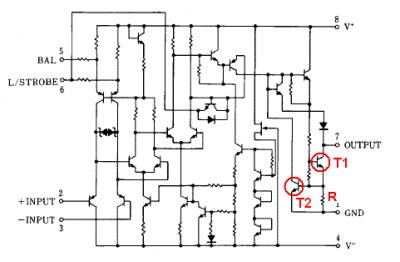

输出接电源似有些怪,但查看NJM311的内部构造可知,1脚GND其实并非是固定的电路“0电位”,比较的结果只是反映在末级驱动管T1的ON/OFF而已,书上的接法等于利用这个芯片在正电源和峰值保持电容之间跨接了一个开关:输入上升至峰值过程中开关ON,让电容快速充电到跟输入电压相等。

放电通路是C1→1MΩ电阻→-15V电源,时间有公式好算;充电则是通过比较器(此时1MΩ的影响已微不足道),比较器里有个限流电路(T2、R),不知道R是多大,但数据手册的“饱和电压”栏中标有Io=50mA的条件可作参考。恒流倒也好算了:根据电流的定义I=Q/t,和电容的定义C=Q/V,消去电荷量Q,即得t=CV/I。