TTL反相器中怎么断定T4是放大状态的?

T3又是截止的话,T4的射极等于什么都没接,根本就说不清是个什么状态,还不如说是“悬浮状态”。(T5在哪儿?指的是T3吧?)

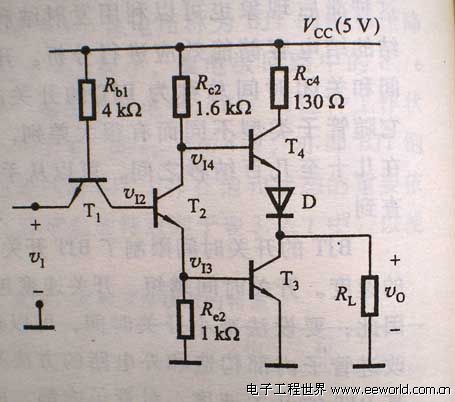

从图上看,当输入低时,T4是处在放大状态的。如果输入υ1足够低,υ12就较低,故:T2基本处于截至态,υ13就低,υ14就高,所以,T3截至,又由于υ14高,故,T4的射极放大输出电路就处于放大状态了。

鲜猫的思路是对的,只是他没有注意图上画出了负载电阻。

这个……可是……不是说了“参考图为去掉上传图中的RL输出电阻”吗?俺没弄明白楼主要以参考图为准,还是以上传图为准说话。:D

“参考图为去掉上传图中的RL输出电阻",没错.

悬浮状态 一说我认为不妥,因为悬浮相当于断开.如果上下都断开,不就相当于高阻态了吗?显然不是啊。

悬浮状态是只可意会的术语,明白意思就可以了,怎么可以成为语言的奴隶:'( :D 你大可不必在这里较执:D关键是在你表述都不准确的情况下 --找不到F5:Q 楼上的各位尽力给你解答了,你不说是否受益:'( 反而:@你不会是在有意识地来考这些热心人的吧:'( :@ :( :D

为什么T4是放大状态而不是导通状态呢?是因为Rc4只有130欧姆吗

当V1=V1H的时候,如果不考虑T2的存在,则应有VB1=V1H+VON=4.1V。显然,在存在T2和T3的情况下,T2和T3的发射极必然同时导通。而一旦T2和T3导通以后,VB1便被钳制在了2.1V,这是为什么?为什么此时VB1被钳制在了2.1V?还有,D的作用是为了确保T3饱和导通时T4可靠地截止,那么D是如何实现此功能的呢?

1、当T2和T3(不是T5)导通,容易看出Vb2=1.4V(2个串联的Vbe),同时Vbc1也是正偏的0.7V,所以加起来是2.1V。

2、如果没有D,Vbe4 = (Vb3 + Vce2 - Vce3),T2、T3饱和时的Vce差不多都是0.2V左右,这样Vbe4≒Vb3≒0.7V,就很难保证T4截止了。

谢谢,可是我还有点不明白。如果Vb1此时为2.1V,可是输入V1=V1H=3.4V,那么T1不会被截至吗?而且如果加上D的话,Vbe4就不等于Vb5+Vce2-Vce5吗?

T1的b-c此时只是一个处于正偏的二极管。

如加上D,Vbe4还要从上式减去D上的压降。

谢谢,我明白了。在输入高电平的情况下,T1始终是截止的对吧