关于PCB铺铜的问题。顶和底层铺铜会不会引起短路

时间:10-02

整理:3721RD

点击:

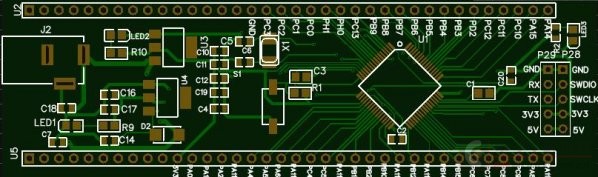

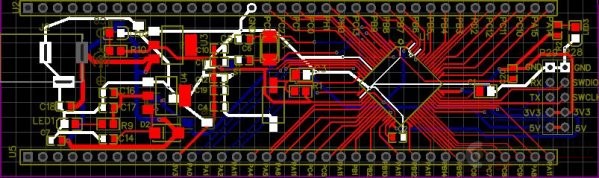

本人基于STM32F4芯片做了一套板子,顶层和底层都铺了铜,顶层连接的网络是VCC(12V供电),底层连接的网络是GND,12V供电经过AMS系列稳压芯片转换为5V和3.3V,电路主要实现的是行列阵列扫描电路实现数据采集功能,可是PCB加工回来后,一测GND和VCC短路了,不知道是什么原因?会不会是顶层和底层铺铜引起的短路啊?铺铜会引起短路么?

先检查PCB源文件两个网络有木有误连接吧

看看

会不会是顶层和底层铺铜引起的短路啊,在制板之前,对pcb作连接性和间距检查都是必须的。你怀疑这个,说明你投板之前都没有认真检查。以后注意。 你看看源文件里有没有短路。铺铜一般铺地。不铺电源。

如果是正常铺的,不会短路,就怕你铺错了

还有种情况,我之前也遇到过。那就是板厂TMD就么有做阻焊。结果,VCC所在的焊盘是做喷锡处理的,锡膏稍稍的溢出焊盘,就跟铜皮短接在一起了。我遇到的这个问题,我也是之前从来没有碰到过。我多次验证才得到这个结论。

还有种情况,那就是你铺铜间距设置太小,一些工艺不好的板厂达不到;

还有,你DRC跑过没有问题?

好的,谢谢各位!这是PCB原理图和二维图。。。

另外,DRC检查没错啊

DRC检查没错啊

铺铜是不会引起短路的,肯定是你的原理图文件出现了错误,好好检查你的原理图文件,还有,一般把电源层和GND放在中间,这样可以尽量保持电源层和GND层的完整