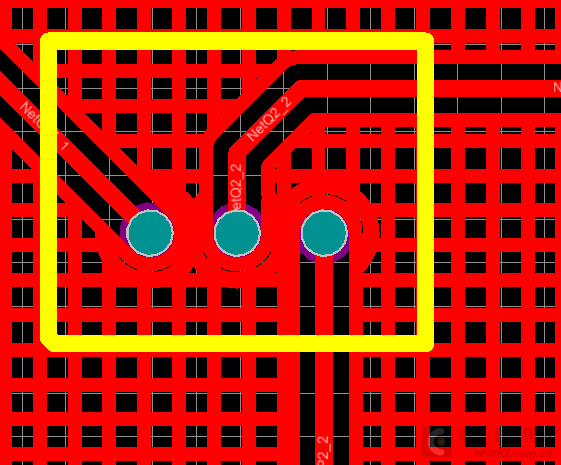

我在敷铜的时候,铜与过孔粘连,这样会导致短路,怎么避免这种状况发生

时间:10-02

整理:3721RD

点击:

file:///C:\Users\Administrator\Documents\Tencent Files\571209944\Image\C2C\B87WEBKLGOFQI)G2P4OJVI.png

规则的间距设置问题or发来源文件帮你看下?

你设置规则就好了,设置敷铜与孔的间距。

调整一下规则,快捷键D R,具体那一项间距的问题,你可以找一下

设置规则

规则里设置下间距就好了 。 暴露QQ号码了

这个不是敷铜规则的问题么?

的确存在异常,如果是电气间距设置太小,可是别处的走线并没有包的那么紧;出错的只是这三个孔,被包住了;

改一下规则里的敷铜与焊盘间距要大于10米尔,你的设定为0.

哈哈哈哈,这都被你发现了

铺铜的规则设置

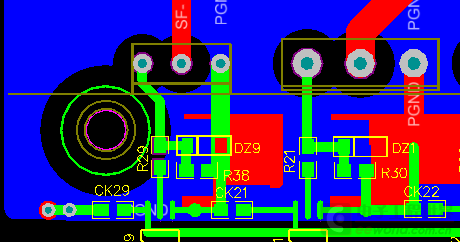

pour over same net polygons only,把同一网络的连在一起。