利用ultra librarian生成cadence元件和封装的方法

时间:10-02

整理:3721RD

点击:

今天跟着@qwqwqw2088的帖子分享用ultra librarian来制作元件库和封装库生成altium designer的方法qwqwqw2088在http://bbs.eeworld.com.cn/thread-428523-1-1.html这个帖子里已经介绍的比较详细了,我就不重复了但是在要利用这个软件生成cadence元件库和allegro封装库的时候遭遇了问题,真心哭死,耗掉了好多时间,总算发现原因了。下面给大家分享一下方法。

前面的步骤跟生成AD的类似,就是要注意下一点,cadence的元件库和封装库是要分开进行的,不知道什么原因。像我一开始很天真的只选择了allegro16.0的,结果找半天就找不到生成的元件,黒线啊,结果是人家只生成封装。

分开介绍下,在选择了相应的软件进行export之后会弹出来一个log.txt出来。你可以按着log里面来操作了。不过我觉得他的log怪怪的。。。。可能我英文不太好。

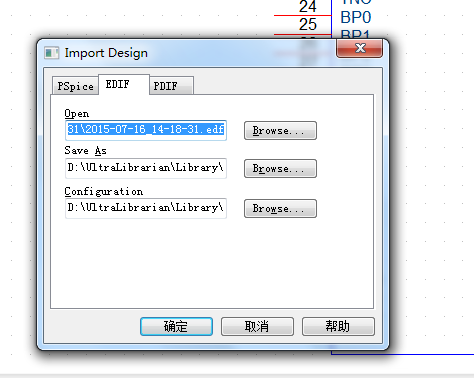

ultra librarian生成的元件库是edf格式的,直接用cadence 打开是无法打开的,要先进行import Design,看截图:

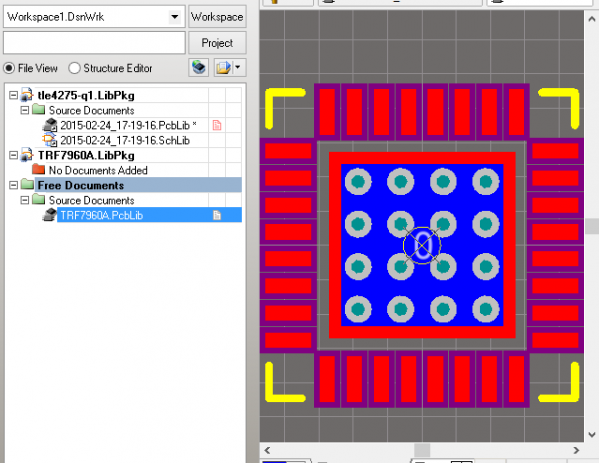

然后讲一下allegro的。其实allegro生成的文件就已经是相应的焊盘,封装文件了,你要做的是把你的封装放进你自己库里面或者你如果不想改动位置,那也要打开user preference在path中添加上相应文件所在的位置,不然软件是会找不到文件的

好啦坑了我一上午的cadence元件和封装生成方法就这么简单结束了。。所以我更想吐血了。

借上图为ultra librarian导入的,针对封装有个问题,能不能直接定义好该封装所有的过孔和顶层、底层PAD为 GND或者是同一网络?

要不然每次导入PCB都要自己添加网络好麻烦,不然标绿

前面的步骤跟生成AD的类似,就是要注意下一点,cadence的元件库和封装库是要分开进行的,不知道什么原因。像我一开始很天真的只选择了allegro16.0的,结果找半天就找不到生成的元件,黒线啊,结果是人家只生成封装。

分开介绍下,在选择了相应的软件进行export之后会弹出来一个log.txt出来。你可以按着log里面来操作了。不过我觉得他的log怪怪的。。。。可能我英文不太好。

ultra librarian生成的元件库是edf格式的,直接用cadence 打开是无法打开的,要先进行import Design,看截图:

然后讲一下allegro的。其实allegro生成的文件就已经是相应的焊盘,封装文件了,你要做的是把你的封装放进你自己库里面或者你如果不想改动位置,那也要打开user preference在path中添加上相应文件所在的位置,不然软件是会找不到文件的

好啦坑了我一上午的cadence元件和封装生成方法就这么简单结束了。。所以我更想吐血了。

扫一扫,关注 EEWORLD 微信订阅号

行业资讯、电子趣闻、技术干货、精彩活动……尽可掌握

之前一直都是使用ultra librarian 配合Altium Designer使用的,非常的好用。

借上图为ultra librarian导入的,针对封装有个问题,能不能直接定义好该封装所有的过孔和顶层、底层PAD为 GND或者是同一网络?

要不然每次导入PCB都要自己添加网络好麻烦,不然标绿

ultra上面估计不行,不过我有个建议你可以去更改元件库,对应的加一个0pin,画原理图的时候接上GND就好了。

这个工具好用,TI的芯片都支持提供数据文件,我每次用到TI芯片,用这个软件生成的封装都很方便

楼主很给力,给后来人涨经验了

倒腾了一天,终于好了,多谢楼主,前面报错不用理就行了

原来是这样啊,谢谢,学了一招。

我的还是解决不了啊 谁知道怎么解决!!

我也弄了一天 了 还没搞定 版主有什么方法可以指导我一下吗