不用画电路图就能设计PCB——用Python画PCB!

请你现在想想,自己在绘制PCB的时候,都是怎样的过程?

包括小编在内,大部分朋友在设计自己的电路板的时候,都要经历从原理图设计开始、连接原理线路、生成网络表进而生成pcb设计。在刚刚开始电子设计的时候,确实大家都很能够理解这样的过程。但是在学习和设计的经历逐渐进步之后,我们渐渐地在设计一些简单的PCB的时候喜欢直接开始PCB设计……

有没有一种方法,不需要设计原理图,就可以直接生成PCB,而且还能够设计出更加复杂的PCB?

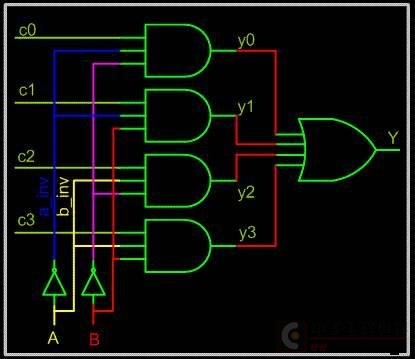

小编在学习fpga的verilog语言的时候,就隐隐约约的感觉到了利用语言来形成电路的力量。而现在,这种方式终于转变成了一种非常普及的力量:利用Python来“形容”电路。

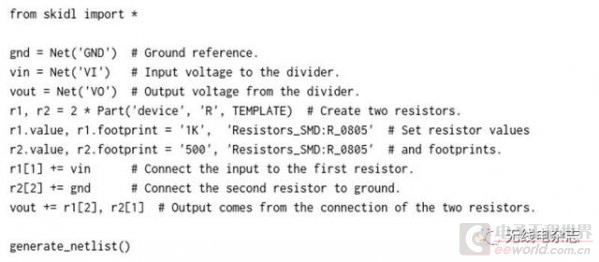

SKiDL是Python的一个库。利用它所提供的函数所形成的代码在执行后可以直接生成KiCAD所能识别的网表文件。你所需要做的事情就是使用自己的大脑,想清楚自己要做的事情是什么、引脚和引脚间的连接方式是什么,然后通过特别编写的函数就可以实现直接书写代码来形成逻辑上的电路了。是不是和硬件描述语言非常类似?

实际上,不管是SKiDL还是Verilog亦或是原理图,它传达给软件的都是对硬件电路的情况的一种描述,只是利用源代码的形式来形容系统的组成有着各种各样的好处,比如支持复用:你不再需要复制粘贴部分原理图,只需要将这部分电路封装成一段子程序,然后规定好模块的出入口。 即可多次复用。从某种意义上来说,使用语言描述电路的方法也能够实现更加方便的电路分享。能够通过复制粘贴的方式简单的共享一个复杂的电路,这也是原理图难以做到的。

虽然这款Python库仍然还处于试行和不断丰富中的状态,但是小编已经摩拳擦掌准备实战一场了,你喜欢这种描述电路的方式吗?

有时候图形的思考速度远快于逻辑的思考速度。各有优缺点吧,主要看应用环境。

利用Python来“形容”电路 -------- 这倒也是个方法,具体实用与否,还需要实践检验

这么屌,白大侠 实践一下

即使是verilog来描述硬件电路,做ASIC也需要后端版图设计啊

还不会python呢

这个会不会太烧脑了?

如果用python,肯定要安装支持的图形库

这只是网表的一种描述形式,离 schematic 还是差很多的,它没有写出来哪个元件的位置在什么地方,朝向如何。用工具自动把网表可视化是有意思的事情,可是出什么结果就不保证了。

板级的EDA通常是这样的:

原理图 --> 网表 --> PCB布局

原理图是人工摆放出来的,小规模的电路特别是模拟电路,直接摆元件,边摆边连线比较符合思维习惯,和纸上画差不多。如果是不用草稿纸,直接写出 SPICE 网表,就太锻炼大脑的能力了

网表文件只保留连接关系,要逆向到原理图比较有难度,假如有交互式的工具帮助干这个我会很喜欢。

从网表到PCB布局除了需要考虑封装尺寸外,还不能交叉走线,比原理图更困难。这个就要更多体力活。又时候不复杂的地方用下自动布线成功了就觉得很爽了。

确实很新颖。

以前做过特别简单的人脸识别,利用opencv库,使用Python语言完成。

期待大神的实践。

这只能叫设计网表

这个想法很酷

不需要设计原理图,就可以直接生成PCB,而且还能够设计出更加复杂的PCB?