PCB设计必看:如何减少错误并提高效率!

时间:10-02

整理:3721RD

点击:

电路板设计是一项关键而又耗时的任务,出现任何问题都需要工程师逐个网络逐个元件地检查整个设计并且消耗过多的检查工作时间,也会导致后期生产贴片良率造成影响,间接的提高了产品成本。可以说电路板设计要求的细心程度不亚于芯片设计。

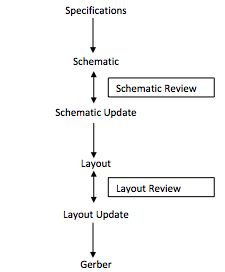

典型的电路板设计流程由以下步骤组成:

前面三个步骤花的时间最多,因为原理图检查是一个手工过程。想像一个具有1000条甚至更多连线的soc电路板。人工检查每一根连线是冗长乏味的一项任务。所有,我们必须重视原理图库和PCB库的重要性,而我比较喜欢去派尔library设计平台去申请各类的库文件,能帮我就是他们那平台提供的正确、标准画的库。事实上,检查每根连线几乎是不可能的,因而会导致最终电路板出问题,比如错误的连线、悬浮节点等。

原理图捕获阶段一般会面临以下几类问题:

● 下划线错误:比如ApllVDD和APLL_VDD

● 大小写问题:比如VDDE和vdde

● 拼写错误

● 信号短路问题

● ……还有许多

为了避免这些错误,应该有种方法能够在几秒的时间内检查完整个原理图。这个方法可以用原理图仿真来实现,而原理图仿真在目前的电路板设计流程中还很少见到。通过原理图仿真可以在要求的节点观察最终输出结果,因此它能自动检查所有连接问题。

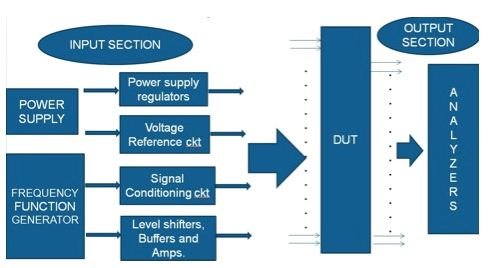

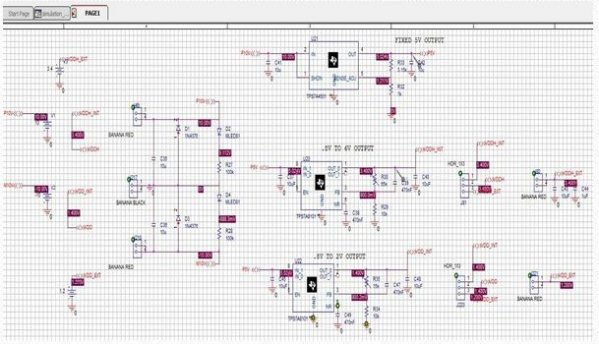

下面通过一个项目实例进行解释。考虑电路板的一个典型框图:

在复杂的电路板设计中,连线数量可能达到数千条,而极少量的更改很可能浪费许多时间去检查。

原理图仿真不仅能节省设计时间,而且能提高电路板质量,并且提高整个流程的效率。

一个典型的待测设备(DUT)具有以下一些信号:

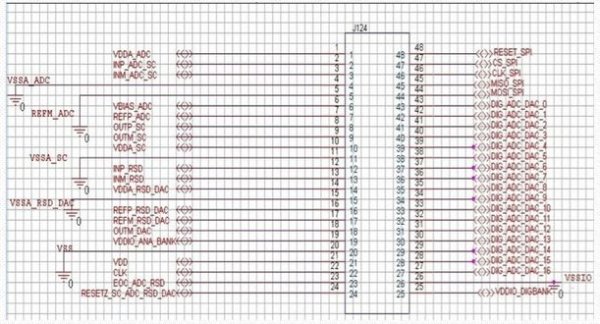

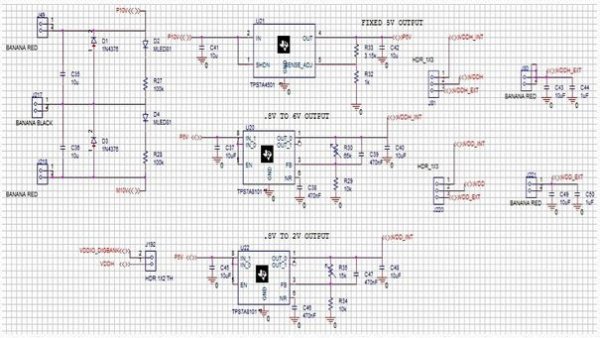

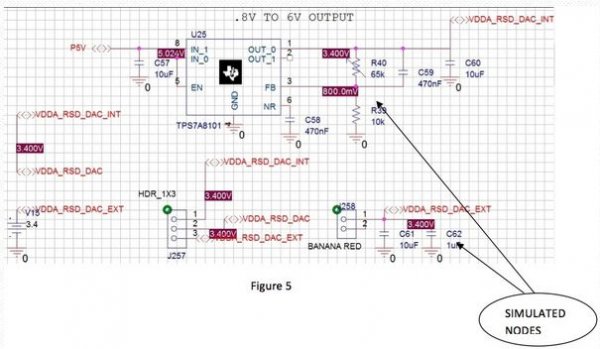

待测设备在经过某些预调整后会有各种各样的信号,并且有各种模块,如稳压器、运放等,用于信号调整。考虑通过稳压器得到的一个供电信号例子:

为了验证连接关系并执行整体检查,使用了原理图仿真。原理图仿真由原理图创建、测试平台创建和仿真组成。

在测试平台创建过程中,将有激励信号给到必要的输入端,然后在感兴趣的信号点观察输出结果。

可以通过将探针连接到待观察节点实现上述过程。节点电压和波形可以指示原理图有没有错误。所有信号连接都会得到自动检查。

让我们看一下上面这张图的一个局部,其中探测的节点和电压清晰可见:

因此在仿真的帮助下,我们可以直接观察结果,确认电路板原理图是否正确。另外,通过仔细调节激励信号或元件值还可以实现设计更改的调查。因此原理图仿真可以节省电路板设计和检查人员的大量时间,并且增加设计正确性的机会。

如果看了此文章的同学感到各样疑问可以提出,或者不想从事检查这些繁琐的事情,你们必须拥有正确性、标准的元件库已做基础。个人推荐派尔library设计平台的库。

不喜勿喷,仅仅奉献给有需要的人看。

典型的电路板设计流程由以下步骤组成:

前面三个步骤花的时间最多,因为原理图检查是一个手工过程。想像一个具有1000条甚至更多连线的soc电路板。人工检查每一根连线是冗长乏味的一项任务。所有,我们必须重视原理图库和PCB库的重要性,而我比较喜欢去派尔library设计平台去申请各类的库文件,能帮我就是他们那平台提供的正确、标准画的库。事实上,检查每根连线几乎是不可能的,因而会导致最终电路板出问题,比如错误的连线、悬浮节点等。

原理图捕获阶段一般会面临以下几类问题:

● 下划线错误:比如ApllVDD和APLL_VDD

● 大小写问题:比如VDDE和vdde

● 拼写错误

● 信号短路问题

● ……还有许多

为了避免这些错误,应该有种方法能够在几秒的时间内检查完整个原理图。这个方法可以用原理图仿真来实现,而原理图仿真在目前的电路板设计流程中还很少见到。通过原理图仿真可以在要求的节点观察最终输出结果,因此它能自动检查所有连接问题。

下面通过一个项目实例进行解释。考虑电路板的一个典型框图:

在复杂的电路板设计中,连线数量可能达到数千条,而极少量的更改很可能浪费许多时间去检查。

原理图仿真不仅能节省设计时间,而且能提高电路板质量,并且提高整个流程的效率。

一个典型的待测设备(DUT)具有以下一些信号:

待测设备在经过某些预调整后会有各种各样的信号,并且有各种模块,如稳压器、运放等,用于信号调整。考虑通过稳压器得到的一个供电信号例子:

为了验证连接关系并执行整体检查,使用了原理图仿真。原理图仿真由原理图创建、测试平台创建和仿真组成。

在测试平台创建过程中,将有激励信号给到必要的输入端,然后在感兴趣的信号点观察输出结果。

可以通过将探针连接到待观察节点实现上述过程。节点电压和波形可以指示原理图有没有错误。所有信号连接都会得到自动检查。

让我们看一下上面这张图的一个局部,其中探测的节点和电压清晰可见:

因此在仿真的帮助下,我们可以直接观察结果,确认电路板原理图是否正确。另外,通过仔细调节激励信号或元件值还可以实现设计更改的调查。因此原理图仿真可以节省电路板设计和检查人员的大量时间,并且增加设计正确性的机会。

如果看了此文章的同学感到各样疑问可以提出,或者不想从事检查这些繁琐的事情,你们必须拥有正确性、标准的元件库已做基础。个人推荐派尔library设计平台的库。

不喜勿喷,仅仅奉献给有需要的人看。

学到了,一些基本的知识点,对自己有莫大的帮助,也记住了电路板设计的流程。

还是需要感谢楼主分享这个好资源。

挺好的资料,非常好,很好。

资料还行,能接受,新手一枚路过

为啥感觉前面回复的都是水军就没一个眼熟的

学到老活到老 ,谢谢大神的干货分享

资料还行,能接受,新手一枚路过

世界上那些最容易的事情中,拖延时间最不费力。