通信系统中,差分滤波器如何布局?

RF工程师在设计中常常会看到单端50Ω系统。有人认为,差分电路很难设计、测试和调试。另一方面,为了提高性能,通信系统常常要应用差分系统,尤其是IF级中。在这些困难中,差分滤波器是一个关键问题。

那么,问题来了——在通信系统中,差分滤波器该如何布局?

一起来看看adi技术牛人Mercy Chen的建议吧

成对差分走线的长度须相同

此规则源自这一事实:差分接收器检测负信号和正信号在哪里同时跨过彼此,即交越点。因此,信号须同时到达接收器才能正常工作。

差分对内的走线布线须彼此靠近,如果一对中的相邻线路之间的距离大于电介质厚度的2倍,则其间的耦合会很小。此规则也是基于差分信号相等但相反这一事实,如果外部噪声同等地干扰两个信号,则其影响会互相抵消。

同样,如果走线并排布线,则差分信号在相邻导线中引起的任何干扰噪声都会彼此抵消。同一差分对内的走线间距在全长范围内须保持不变。如果差分走线彼此靠近布线,则会影响总阻抗。如果此间距在 驱动器与接收器之间变化不定,则一路上会存在阻抗不匹配,导致反射。

差分对之间的间距应较宽,以使其间的串扰最小

如果在同一层上使用铜填充,应加大从差分走线到铜填充之间的间。推荐最小间隙为走线到铜填充的走线宽度的3倍。

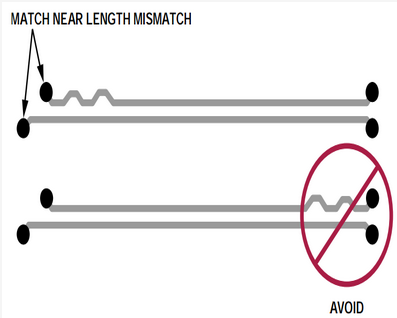

在靠近差分对内偏斜源处引入少量弯弯曲曲的校正,从而降低这种偏斜(参见图1)。

图1. 使用弯曲校正

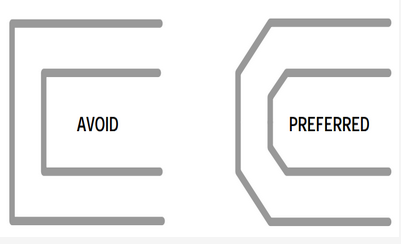

差分对布线时,应避免急转弯(90°)(参见图2)。

图2. 避免90°弯曲

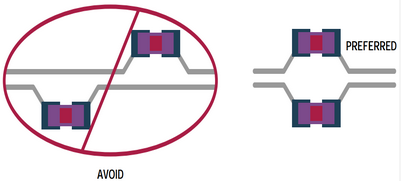

差分对布线时,应使用对称布线(参见图3)。

图3. 对称布线指南

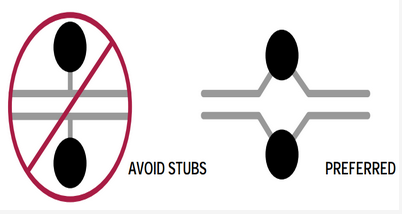

若需要测试点,应避免引入走线分支,而且测试点应对称放置(参见图4)。

图4. 避免走线分支

考虑降低对滤波器元件值的要求,减少印刷电路板(PCB)上的调谐工作量,寄生电容和电感应尽可能小

与滤波器设计中的电感设计值相比,寄生电感可能微不足道。寄生电容对差分IF滤波器更为重要。IF滤波器设计中的电容只有几pF,如果寄生电容达到数十分之一pF,滤波器响应就会受到相当大的影响。为了避免寄生电容影响,一个良好的做法是避免差分布线区域和电源扼流圈下有任何接地或电源层。

差分电路PCB布局设计示例

ADI接收器参考设计板(参见图5)提供了差分滤波器PCB布局的一个示例。图中显示ADL5201和AD6649之间有一个五阶滤波器。

AD6649是一款14位250 MHz流水线式ADC,具有非常好的SNR性能哦!

图5. 差分电路PCB布局设计示例

本文摘自ADI应用笔记《通信系统中接收链的差分滤波器设计》

扫一扫,关注 EEWORLD 微信订阅号

行业资讯、电子趣闻、技术干货、精彩活动……尽可掌握

差分走线的方法大家可以了解一下