在满足安全间距0.5mm,元器件两引脚间的铺铜是不是应该挖掉?

时间:10-02

整理:3721RD

点击:

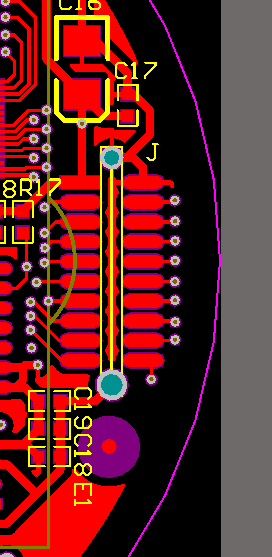

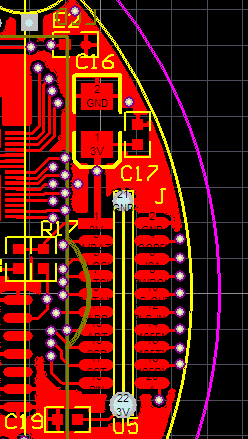

在满足安全间距0.5mm,元器件两引脚间的铺铜是不是应该挖掉?不挖掉有没有什么影响,或者是安全隐患?是应该如图左还是如图右?

这个不一定的,要看你这些元器件以及引脚的实际应用情况。

在真正的设计中,各个网络的电压不同、电气特性不同,其实应该分别应用不同的安全间距。

习惯上会分成几个不同的Net Class,分别设定安全间距规则。

要是我就选择右图,因为覆铜没有违反规则,如果不好用在选择前者,一般高频地有影响,通常的电路,不用考虑

那元件引脚间铺铜到底有没有大影响?比如3258封装10uF钽电容,用于3V电源上。

其实我个人习惯用mil来描述,如果是我的话,我会选择右边那种,左边虽有铜,但是有些铜可能会造成天线效应。(有可能会成为孤铜哦)

恩,左边有孤铜我觉得是因为地采用线连,问题又来了,地是线连好还是块连好,线连电流走向以控制,块连面积比较大

地的连接,请在每个原件的gnd网络下打个地过孔并连接,这样到时候铺铜就可以和这些过孔形成同一个网络了。孤立的地,请用走线连接。不知道您了解我说的吗?

恩,了解了,非常感谢!