Protel DXP PCB设计这是什么错误?

时间:10-02

整理:3721RD

点击:

Protel Design System Design Rule Check

PCB File : \ALTIUM2004_EAXAMPLE\28335底板0520重新布局\replace_ep3c25.PcbDoc

Date : 2015/5/21

Time : 8:24:18

Processing Rule : Hole Size Constraint (Min=0mil) (Max=1000mil) (All)

Rule Violations :0

Processing Rule : Height Constraint (Min=0mil) (Max=1000mil) (Prefered=500mil) (All)

Rule Violations :0

Processing Rule : Width Constraint (Min=5mil) (Max=100mil) (Preferred=10mil) (All)

Rule Violations :0

Processing Rule : Clearance Constraint (Gap=5mil) (All),(All)

Rule Violations :0

Processing Rule : Broken-Net Constraint ( (All) )

Rule Violations :0

Processing Rule : Short-Circuit Constraint (Allowed=Yes) (All),(All)

Rule Violations :0

Violations Detected : 15

Time Elapsed : 00:00:02

PCB File : \ALTIUM2004_EAXAMPLE\28335底板0520重新布局\replace_ep3c25.PcbDoc

Date : 2015/5/21

Time : 8:24:18

Processing Rule : Hole Size Constraint (Min=0mil) (Max=1000mil) (All)

Rule Violations :0

Processing Rule : Height Constraint (Min=0mil) (Max=1000mil) (Prefered=500mil) (All)

Rule Violations :0

Processing Rule : Width Constraint (Min=5mil) (Max=100mil) (Preferred=10mil) (All)

Rule Violations :0

Processing Rule : Clearance Constraint (Gap=5mil) (All),(All)

Rule Violations :0

Processing Rule : Broken-Net Constraint ( (All) )

Rule Violations :0

Processing Rule : Short-Circuit Constraint (Allowed=Yes) (All),(All)

Rule Violations :0

Violations Detected : 15

Time Elapsed : 00:00:02

这不是错误

所有的违反规则为0

请问这15个违反的是哪个规则怎么查找呢

哦,后面还有Violations Detected : 15

违规的部分都会呈现绿色。

这个应该能找到吧

Violations Detected : 15是什么?

我试了试,将两根不同网络的线联通 15就变成16了,其他不变

Violations Detected : 15是什么?

我试了试,将两根不同网络的线联通 15就变成16了,其他不变

我检查了好久,但没找到类似的交叉的网络了

一般错误会在上面显示出来啊

软件这里真是个奇葩的结论

板子有么有变绿的地方?在绿告警地方双击可以看,但不知道这个早期版本Protel DXP PCB有没有这个功能

没有变绿

或者是报的错没有看见,对照规则检查一下

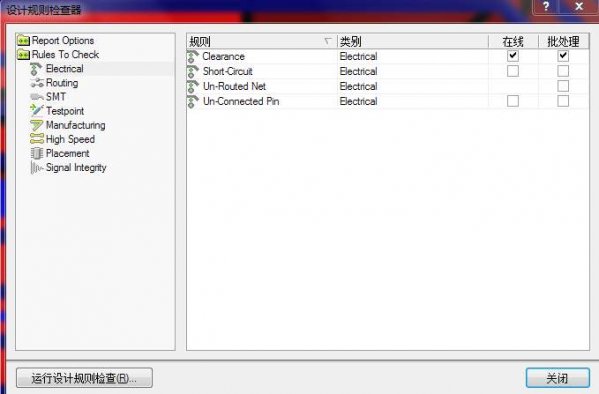

终于解决了,如图:规则检查中Electrical 中如果全勾选就出现我遇到的问题的结果,如果之勾选图中的第一行,则会提示违规处的坐标

都是规则错误了

为什么还这么坚守Protel DXP PCB 这个版本好久了

从简单的开始学嘛。

AD哪个版本比较稳定好用?

AD9以上都可以,,,

初学者就慢慢来吧,,版本其实不重要,就是一个画图工具,熟练掌握就行