在一般的推挽电路中为什么考虑电路负载时常用容性负载,而不是阻性或感性?

看不到图,忘发了吧?

楼主说推挽电路,估计是放大器。放大器考虑负载,应该按照实际情况来确定,从来没有“常用”一说。

file:///C:\Users\WJY\AppData\Roaming\Tencent\Users\352137251\QQ\WinTemp\RichOle\0VWHZW66]6$GG)`@UQ1N)77.png

没办法解答。

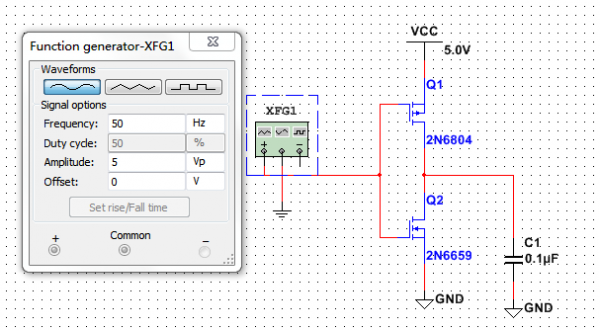

这是仿真图,负载(0.1uF电容)很可能是仿真者随意放上去的,并不能代表“一般”情况。

那就不管图吧,就是一个CMOS反相器中,为什么在考虑电路负载时常考虑容性负载?

刚刚才弄清楚,你说的是CMOS数字电路。

CMOS数字电路的输出通常是下一级数字电路,下一级如果也是CMOS数字电路的话,因为CMOS输入端是MOS管的门极,其输入特性就是电容性的,所以考虑负载时把下一级输入简化成一个电容(不过也没有0.1uF那么大,通常每个门10pF上下,至多几十pF)。

但若下一级是TTL数字电路,则其输入特性并不是电容性,而是电阻性居多。不过现在TTL数字电路已经很少使用,COMS工艺芯片占绝大多数。

如果下一级芯片是其它电路,例如分立三极管构成的放大器,当然也不能认为其输入为电容性。如果是喇叭或者蜂鸣器之类,甚至可能是个谐振回路,情况更复杂,必须具体情况具体分析。

只有CMOS工艺芯片互联,才可以将负载当成一个小电容来考虑。

先说明容性负载和感性负载不是首先看是否是CMOS

阻止电流流过,也可储能在电容中的一般是容性负载,,,

楼主应该交待清楚问题的前提,“常用的推挽电路”一说通常特指放大器,比如甲乙类音频功放、运算放大器等等就属于这类,其负载大都是阻性的,容性负载几乎没有。而楼主问题涉及的却是逻辑门电路的内电路,这时当然情况完全不同,这里的推挽电路是数字电路中的一部分,根本不是放大器。就CMOS门电路而言,其负载通常也是CMOS电路,CMOS电路的输入阻抗极高,可以认为是开路,但MOS管的栅极具有一定的电容量,CMOS电路的耗电很大程度上与MOS管的栅容充放电有关,这时的电路模型自然是容性负载,而这是CMOS电路的特征,根本不可说什么“推挽电路的负载通常为容性”。

多谢指导。

多谢指导

多谢指导

好帖!

好帖!