原理图编译警告问题

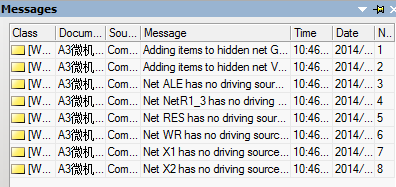

1.Adding items to hiden net GND;

2.Adding items to hiden net VCC;

3.NET ALE has no driving source;

请问这个警告怎么修改呢?谢谢大神了!

一般为使用的元件库有问题,或走线有误,没有网络标号

可是我编译没有出错,只有这个警告啊..难道说这个警告意思就是有错误?嗯嗯,好吧,我再查查.谢谢啦!

不知你用的是什么软件。看看ALE 网络的连接,线的两端是不是都有元件。。。。

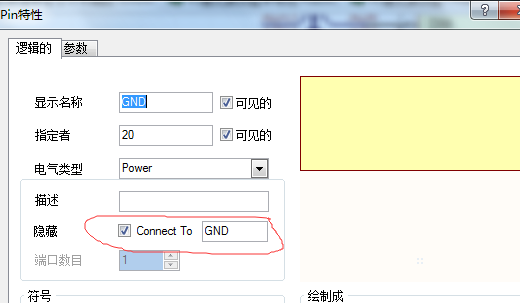

第一个跟第二个问题应该是你原理图里面有元件的power管脚被隐藏了,没连接上,比如一些集成运算的VDD脚和GND脚。

第三个问题是不是你的原理图是free doc模式下编译呢?要放到project里面进行编译应该就可以了。

还得问一下,那些集成的芯片的默认隐藏的电源和地的引脚不是自动连接到电源和地吗?难道还要重现显示,然后重新连接?这个我再试试。第三第四个问题,我之前遇到过类似你说的现象,现在已经确认加在一个工程里面,可是还是有同样的错误。

哦,我用 的是altium designer 6.9

第一个和第二个问题我还是建议不要隐藏自己连接一下看看,记得是可以自动连接的,但是有碰到过这种没有自动连接要手动连接的情况,具体原因可能是软件bug。还有可能就是你自动连接的时候设置对了连接网络嘛?

第三个问题我又去看了下,可能是你的管脚设置成了输入管脚,那在生成的时候就要求有输入信号,一种办法是把管脚改成passive类型,另外一种方法就是设置ERC规则屏蔽。

谢谢,后几个问题都是因为想简化电路,用了网络标号,但电路是对的。后来去掉了网络标号,用信号线连接,就没有错误了。

第一二个问题,软件对器件的默认设置就是上面那个引脚的图那样,只能把那些引脚都显示出来,接上VCC和GND,就没问题了。

但我的解决办法是修改警告规则,把adding items to hiden net 这个规则给更改成 no report的。因为我的原理图中这种需要内部驱动的器件太多了,图纸也不够大,不适合一个一个显示再连接。

谢谢你能回复我,给我很大帮助!谢谢!