展频对电磁兼容的影响

时间:10-02

整理:3721RD

点击:

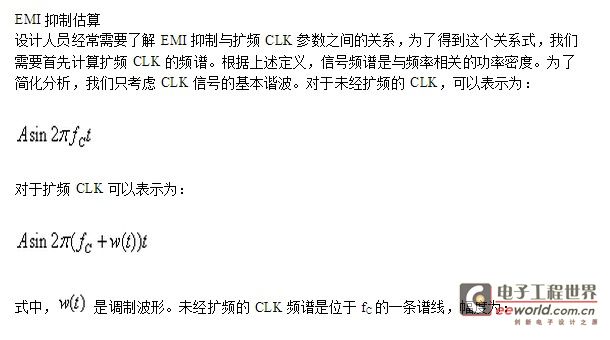

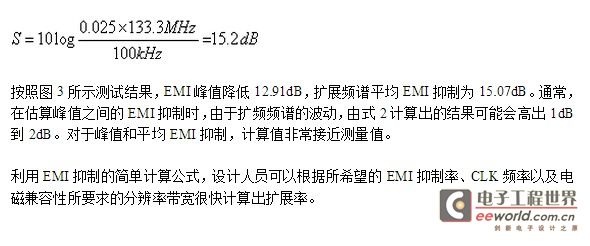

降低电磁干扰(EMI)是电子系统设计人员需要考虑的一个重要因素,扩频时钟(clk)为降低EMI提供了一个有效途径。本文给出了扩频CLK的定义和估算EMI抑制性能的简单公式。所提供的公式经过Maxim CLK发生器MAX9492的数据验证。

数字信号有两种主要形式:数字数据和数字时钟(CLK)。

数字信号是当前数字电子产品中的主要信号形式,通常为单端信号,CMOS或ttl电平。我们观察到的数字信号一般是一串宽度不同的脉冲,时钟信号通常是具有相同脉宽的矩形脉冲。

数字信号和CLK信号的频谱成份包含有高次谐波,信号本身及其谐波共同在电子系统内部和系统之间产生了电磁干扰(EMI)。降低EMI的一条简单、有效途径是使CLK频率产生抖动[1, 2]。本应用笔记介绍了扩频CLK (MAX9492),并提供了一种利用时钟参数指标快速计算EMI抑制的方法。

扩频CLK: 定义和测量

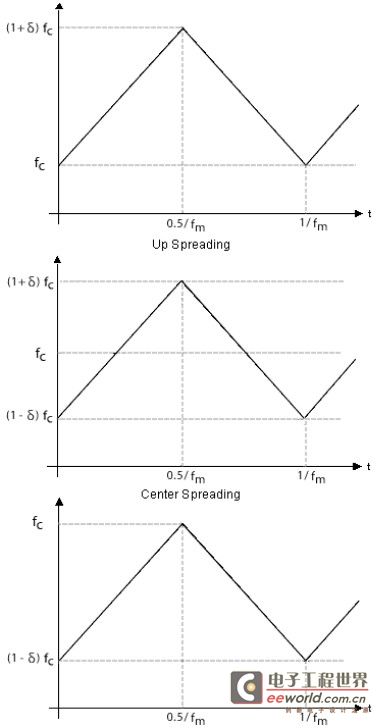

为了考察抖动时钟的扩展频谱,我们定义了以下扩频CLK参数:扩展率、扩频类型、调制率和调制波形。扩展率是频率抖动(或扩展)范围与原CLK频率(fC)的比值。扩频类型指向下扩频、中心扩频或向上扩频。假设扩频范围为∆f,则扩展率定义为:

调制率,fm,用于确定CLK频率扩展周期率,在该周期内CLK频率变化∆f 并返回到初始频率。调制波形代表CLK频率随时间的变化曲线,通常为锯齿波。

图1给出了调制波形及其与 和fm的关系式

图1. 扩频CLK频谱

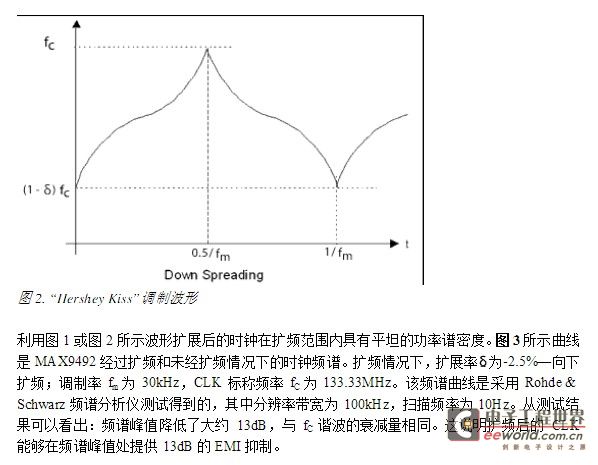

为了得到平坦的CLK频谱,一种称为“Hershey Kiss™,”的特殊曲线被用作调制波形(图2)

数字信号有两种主要形式:数字数据和数字时钟(CLK)。

数字信号是当前数字电子产品中的主要信号形式,通常为单端信号,CMOS或ttl电平。我们观察到的数字信号一般是一串宽度不同的脉冲,时钟信号通常是具有相同脉宽的矩形脉冲。

数字信号和CLK信号的频谱成份包含有高次谐波,信号本身及其谐波共同在电子系统内部和系统之间产生了电磁干扰(EMI)。降低EMI的一条简单、有效途径是使CLK频率产生抖动[1, 2]。本应用笔记介绍了扩频CLK (MAX9492),并提供了一种利用时钟参数指标快速计算EMI抑制的方法。

扩频CLK: 定义和测量

为了考察抖动时钟的扩展频谱,我们定义了以下扩频CLK参数:扩展率、扩频类型、调制率和调制波形。扩展率是频率抖动(或扩展)范围与原CLK频率(fC)的比值。扩频类型指向下扩频、中心扩频或向上扩频。假设扩频范围为∆f,则扩展率定义为:

调制率,fm,用于确定CLK频率扩展周期率,在该周期内CLK频率变化∆f 并返回到初始频率。调制波形代表CLK频率随时间的变化曲线,通常为锯齿波。

图1给出了调制波形及其与 和fm的关系式

图1. 扩频CLK频谱

为了得到平坦的CLK频谱,一种称为“Hershey Kiss™,”的特殊曲线被用作调制波形(图2)

展频对电磁兼容的影响

真还没有注意过这些问题,,好好看看

不明觉厉