关于四层板设计,电源层的缩进和铺铜问题。求高手指点!

时间:10-02

整理:3721RD

点击:

我是个PCB新手,现在在做四层板,用的是添加Layer,正片铺铜。

下面是我关于电源层缩进的一些疑惑,望高手解答指点。

第一个问题是20H原则,这H是板厚还是什么?点击层,提示copper thickness是1.4mil,那么1.4mil的板厚*20=28mil。个人觉得如果是板厚只有1.4mil不切实际,不懂工艺的说

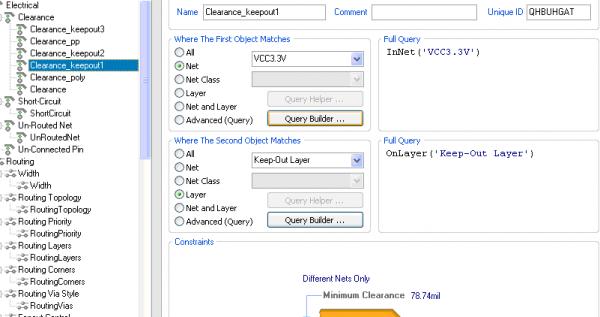

第二个问题,假如说我现在地层已经缩进了一定距离,离板边。那我接下来要缩进电源层,我的理解是POWER层肯定要比GND层还要往里缩,我尝试过在间距里设置铺铜与Keepout层的最小间距来缩进2个层,用的是选NET和选层。可以解决。想问还有别的规则设置方法么?

第三个问题,我也用添加PLANE做过负片。设置了pullback后,但是缩进效果不理想,板的两边缩进不一致,也都不是想要的缩进量。这个是什么原因?

第四个问题,铺铜的时候,可以设置铺铜与铺铜之间安全间距,但是只能保证同一层上的,如果我想要一个不规则的GND层下再铺一层同样不规则近似POWER层,要求同比缩进20mil的间距,有规则可以设置么?

第一次发帖的说,希望问题可以解决,小女子不甚感激啊铺铜缩进设置

下面是我关于电源层缩进的一些疑惑,望高手解答指点。

第一个问题是20H原则,这H是板厚还是什么?点击层,提示copper thickness是1.4mil,那么1.4mil的板厚*20=28mil。个人觉得如果是板厚只有1.4mil不切实际,不懂工艺的说

第二个问题,假如说我现在地层已经缩进了一定距离,离板边。那我接下来要缩进电源层,我的理解是POWER层肯定要比GND层还要往里缩,我尝试过在间距里设置铺铜与Keepout层的最小间距来缩进2个层,用的是选NET和选层。可以解决。想问还有别的规则设置方法么?

第三个问题,我也用添加PLANE做过负片。设置了pullback后,但是缩进效果不理想,板的两边缩进不一致,也都不是想要的缩进量。这个是什么原因?

第四个问题,铺铜的时候,可以设置铺铜与铺铜之间安全间距,但是只能保证同一层上的,如果我想要一个不规则的GND层下再铺一层同样不规则近似POWER层,要求同比缩进20mil的间距,有规则可以设置么?

第一次发帖的说,希望问题可以解决,小女子不甚感激啊铺铜缩进设置

为什么没人理我,好桑心

深刻检讨自己以前只看帖不回帖···

1,20H是指的H是电源层到地层的距离,如果一个6层板的的这两层有可能是0.5mm,那么20H就是10mm的缩进距离了,所以这个距离有些大,一般很少用。

2,你这个是用的AD软件吧,我没用过这个软件,一般建议电源比地稍微缩个0.5mm左右就差不多了,还是具体画个模板来做吧

3&4,没用过AD,不好回答,建议多看看帮助文件,问题没有你想象的复杂,静下心来慢慢多试几次就好了

谢谢,继续看书····