关于cpu接口的屏,时序的确定。

时间:10-02

整理:3721RD

点击:

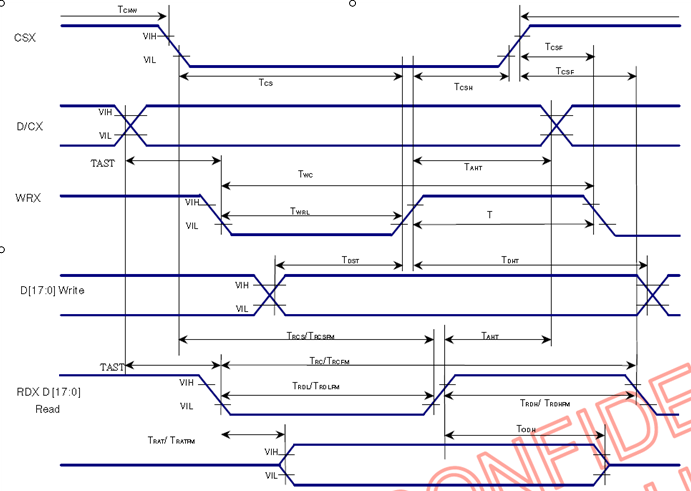

关于cpu接口的屏,时序的确定。有什么对应关系吗?

在lcd.c文件中的init_lcd_interface函数中设置:

// CS to WR setup time,是指片选信号拉低到V1L开始到WRX信号拉低到V1L结束,//等于Tcs – TWRL

SET_LCD_PARALLEL_CE2WR_SETUP_TIME((kal_uint32)2);

// CS to WR hold time,WRX拉高后,片选保持时间,等于TCSH

SET_LCD_PARALLEL_CE2WR_HOLD_TIME(1);

//data write wait state period指的是写信号有效的时间,即拉低的时间,图中的TWRL

SET_LCD_PARALLEL_WRITE_WAIT_STATE(5);

//CS to RD setup time.是指片选有效到读信号的建立时间,图中为TRCS – TRDL

SET_LCD_PARALLEL_CE2RD_SETUP_TIME(2);

//是指读信号被拉低的时间,图中的TRDL /TRDLRM

SET_LCD_PARALLEL_READ_LATENCY_TIME(20);

图在附件中,贴不鸟图

非常感谢!...............