缝隙耦合微带天线带宽问题

时间:10-02

整理:3721RD

点击:

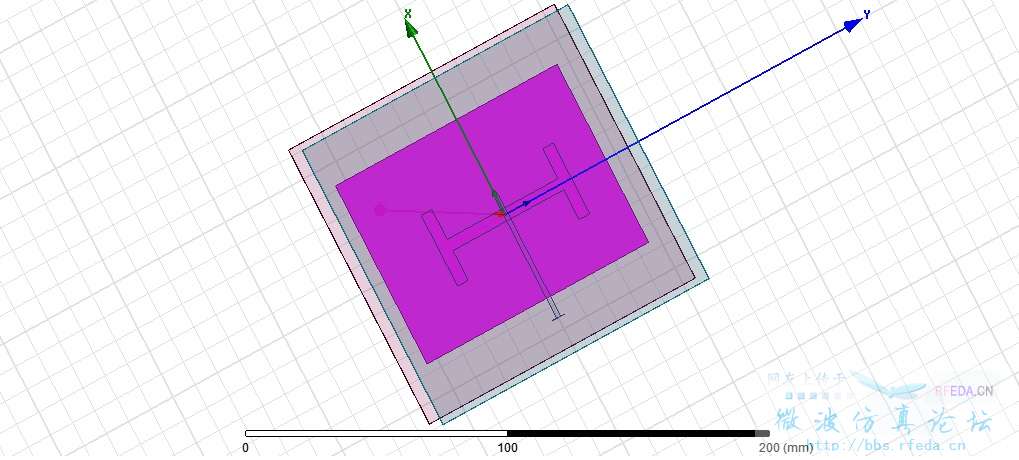

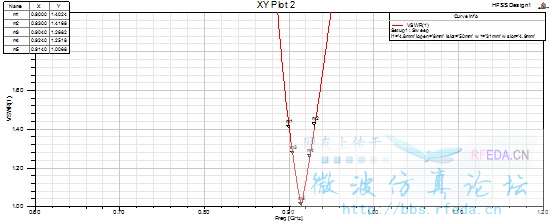

看来不少书和文献都说缝隙耦合微带天线带宽可以做到10%,但是我用HFSS仿真的时候却-10db带宽只能做到1.4%,还是用了hour glass的缝隙,请教大家如何在不提高基板厚度的情况下进一步提升带宽。中心频率1.7GHz,上层2mm(Er=2.55),下层1mm(Er=3.55)

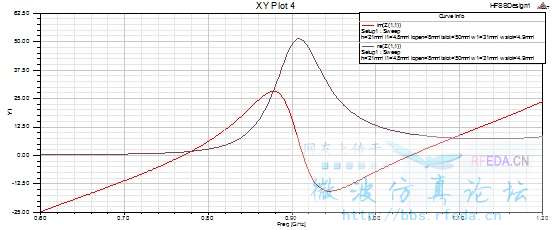

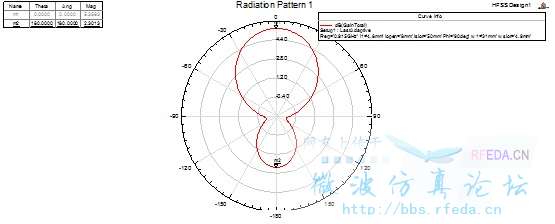

随后把缝宽改为1mm,前后比略有提高(增益7dB,后瓣增益0dB),达不到缝隙耦合天线前后比的典型值 15-20dB

驻波阻抗恶化,观察到双谐振现象

木有人来看看吗

刚好最近也在做缝隙耦合馈电的微带天线,阻抗带宽和上层介质的厚度、介电常数有关,也和输入阻抗匹配、缝隙耦合能力有关。我也碰到了和小编类似的问题,仿真出来阻抗带宽比小编的好一些,但是前后比很低,完全不像缝隙耦合天线应该有的效果。说点不成熟的看法,如果不想改变上基板厚度的话,把缝隙的位置沿Y方向放在贴片边缘附近,试试效果如何。有种说法是缝隙放在贴片边缘,相比放在贴片中心时的耦合量更大。继续调匹配,第一张图直观上感觉缝隙偏小。

最后,还是求助大神来指点,本想开个贴的,看到小编的帖子,搭个顺风车了。

把图贴上来 驻波比的要求是在900-930MHz之间低于1.3 增益6-7dB之间

随后把缝宽改为1mm,前后比略有提高(增益7dB,后瓣增益0dB),达不到缝隙耦合天线前后比的典型值 15-20dB

驻波阻抗恶化,观察到双谐振现象

我试了试在两层介质版之间加入一层空气层,带宽提高了不少,原来只有十几M,现在有80M左右了,但是不知道这样做是不是会提高加工难度。

加空气层相当于增加上基板厚度,降低有效介电常数,所以阻抗带宽更宽了。实际加工中,无非上下基板分开加工,然后在中间想办法固定好。也可以加厚上基板,两层基板紧压在一起,就像你模型中画的一样。

嗯,谢谢了!因为是要做成阵列的,增加基板厚度会使重量变大,看样子只好加空气层了