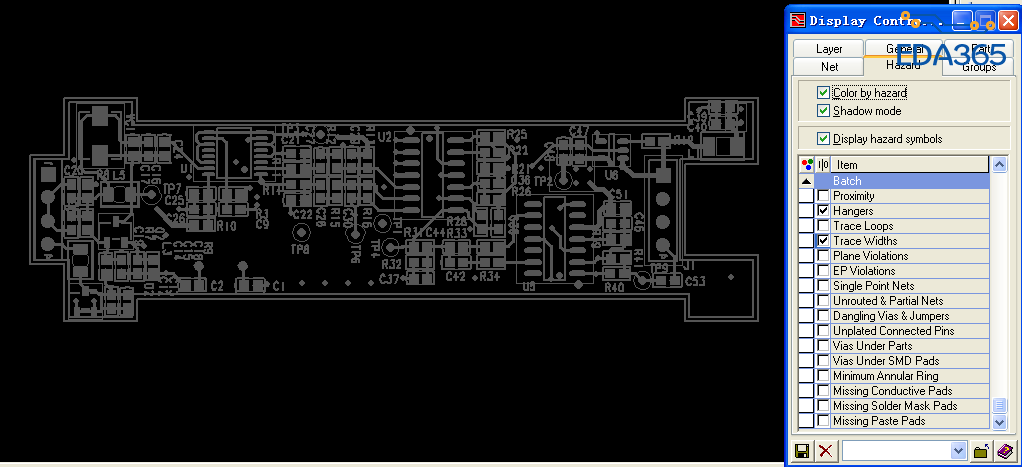

EE7.9.4ЦЬЭКѓ batch DRCМьВщЃЁ

DRC - (Final DRC)

-----------------

04:46 PM Thursday, April 16, 2015

Job Name: E:\WorkSpace\Doppler\Hardware\DS120\PCB\Board1.pcb

---------

PROXIMITY

---------

Use DRC Window : NO

Disable Same Cell Pad-Pad Checks : NO

Enable Same Net Pad-Pad Checks : NO

Layers Specifed To Check : Layer 1

Layer 2

Layer 3

Layer 4

Net Class Clearances And Rules

------------------------------

Components Layer 1 TO Components Layer 1

No Hazards.

Traces Layer 1 TO Traces Layer 1

No Hazards.

Traces Layer 1 TO Part Pads SMD Layer 1

No Hazards.

Traces Layer 1 TO Part Pads Thru Layer 1

No Hazards.

Traces Layer 1 TO Part Holes Layer 1

No Hazards.

Traces Layer 1 TO Via Pads Layer 1

No Hazards.

Traces Layer 1 TO Via Holes Layer 1

No Hazards.

Part Pads SMD Layer 1 TO Part Pads SMD Layer 1

No Hazards.

Part Pads SMD Layer 1 TO Part Pads Thru Layer 1

No Hazards.

Part Pads SMD Layer 1 TO Part Holes Layer 1

No Hazards.

Part Pads SMD Layer 1 TO Via Pads Layer 1

No Hazards.

Part Pads SMD Layer 1 TO Via Holes Layer 1

No Hazards.

Part Pads Thru Layer 1 TO Part Pads Thru Layer 1

No Hazards.

Part Pads Thru Layer 1 TO Part Holes Layer 1

No Hazards.

Part Pads Thru Layer 1 TO Via Pads Layer 1

No Hazards.

Part Pads Thru Layer 1 TO Via Holes Layer 1

No Hazards.

Part Holes Layer 1 TO Via Pads Layer 1

No Hazards.

Part Holes Layer 1 TO Via Holes Layer 1

No Hazards.

Via Pads Layer 1 TO Via Pads Layer 1

No Hazards.

Via Pads Layer 1 TO Via Holes Layer 1

No Hazards.

Via Holes Layer 1 TO Via Holes Layer 1

No Hazards.

Part Pads Thru Layer 2 TO Part Pads Thru Layer 2

No Hazards.

Part Pads Thru Layer 2 TO Part Holes Layer 2

No Hazards.

Part Pads Thru Layer 2 TO Via Pads Layer 2

No Hazards.

Part Pads Thru Layer 2 TO Via Holes Layer 2

No Hazards.

Part Holes Layer 2 TO Via Pads Layer 2

No Hazards.

Part Holes Layer 2 TO Via Holes Layer 2

No Hazards.

Via Pads Layer 2 TO Via Pads Layer 2

No Hazards.

Via Pads Layer 2 TO Via Holes Layer 2

No Hazards.

Via Holes Layer 2 TO Via Holes Layer 2

No Hazards.

Traces Layer 3 TO Traces Layer 3

No Hazards.

Traces Layer 3 TO Part Pads Thru Layer 3

No Hazards.

Traces Layer 3 TO Part Holes Layer 3

No Hazards.

Traces Layer 3 TO Via Pads Layer 3

No Hazards.

Traces Layer 3 TO Via Holes Layer 3

No Hazards.

Part Pads Thru Layer 3 TO Part Pads Thru Layer 3

No Hazards.

Part Pads Thru Layer 3 TO Part Holes Layer 3

No Hazards.

Part Pads Thru Layer 3 TO Via Pads Layer 3

No Hazards.

Part Pads Thru Layer 3 TO Via Holes Layer 3

No Hazards.

Part Holes Layer 3 TO Via Pads Layer 3

No Hazards.

Part Holes Layer 3 TO Via Holes Layer 3

No Hazards.

Via Pads Layer 3 TO Via Pads Layer 3

No Hazards.

Via Pads Layer 3 TO Via Holes Layer 3

No Hazards.

Via Holes Layer 3 TO Via Holes Layer 3

No Hazards.

Components Layer 4 TO Components Layer 4

No Hazards.

Traces Layer 4 TO Traces Layer 4

No Hazards.

Traces Layer 4 TO Part Pads SMD Layer 4

No Hazards.

Traces Layer 4 TO Part Pads Thru Layer 4

No Hazards.

Traces Layer 4 TO Part Holes Layer 4

No Hazards.

Traces Layer 4 TO Via Pads Layer 4

No Hazards.

Traces Layer 4 TO Via Holes Layer 4

No Hazards.

Part Pads SMD Layer 4 TO Part Pads SMD Layer 4

No Hazards.

Part Pads SMD Layer 4 TO Part Pads Thru Layer 4

No Hazards.

Part Pads SMD Layer 4 TO Part Holes Layer 4

No Hazards.

Part Pads SMD Layer 4 TO Via Pads Layer 4

No Hazards.

Part Pads SMD Layer 4 TO Via Holes Layer 4

No Hazards.

Part Pads Thru Layer 4 TO Part Pads Thru Layer 4

No Hazards.

Part Pads Thru Layer 4 TO Part Holes Layer 4

No Hazards.

Part Pads Thru Layer 4 TO Via Pads Layer 4

No Hazards.

Part Pads Thru Layer 4 TO Via Holes Layer 4

No Hazards.

Part Holes Layer 4 TO Via Pads Layer 4

No Hazards.

Part Holes Layer 4 TO Via Holes Layer 4

No Hazards.

Via Pads Layer 4 TO Via Pads Layer 4

No Hazards.

Via Pads Layer 4 TO Via Holes Layer 4

No Hazards.

Via Holes Layer 4 TO Via Holes Layer 4

No Hazards.

Total Hazards Found : 0

Planes Clearances And Rules

---------------------------

Positive Planes Layer 1 TO Part Pads SMD Layer 1

No Hazards.

Positive Planes Layer 1 TO Part Pads Thru Layer 1

No Hazards.

Positive Planes Layer 1 TO Part Holes Layer 1

No Hazards.

Positive Planes Layer 1 TO Positive Planes Layer 1

No Hazards.

Positive Planes Layer 1 TO Route Border

No Hazards.

Positive Planes Layer 1 TO Traces Layer 1

No Hazards.

Positive Planes Layer 1 TO Plane Obstructs Layer 1

No Hazards.

Positive Planes Layer 1 TO Via Pads Layer 1

No Hazards.

Positive Planes Layer 1 TO Via Holes Layer 1

No Hazards.

Positive Planes Layer 2 TO Part Pads Thru Layer 2

No Hazards.

Positive Planes Layer 2 TO Part Holes Layer 2

No Hazards.

Positive Planes Layer 2 TO Route Border

No Hazards.

Positive Planes Layer 2 TO Via Pads Layer 2

No Hazards.

Positive Planes Layer 2 TO Via Holes Layer 2

No Hazards.

Positive Planes Layer 3 TO Part Pads Thru Layer 3

No Hazards.

Positive Planes Layer 3 TO Part Holes Layer 3

No Hazards.

Positive Planes Layer 3 TO Positive Planes Layer 3

No Hazards.

Positive Planes Layer 3 TO Route Border

No Hazards.

Positive Planes Layer 3 TO Traces Layer 3

No Hazards.

Positive Planes Layer 3 TO Trace Obstructs Layer 3

No Hazards.

Positive Planes Layer 3 TO Via Pads Layer 3

No Hazards.

Positive Planes Layer 3 TO Via Holes Layer 3

No Hazards.

Positive Planes Layer 4 TO Part Pads SMD Layer 4

No Hazards.

Positive Planes Layer 4 TO Part Pads Thru Layer 4

No Hazards.

Positive Planes Layer 4 TO Part Holes Layer 4

No Hazards.

Positive Planes Layer 4 TO Positive Planes Layer 4

No Hazards.

Positive Planes Layer 4 TO Route Border

No Hazards.

Positive Planes Layer 4 TO Traces Layer 4

No Hazards.

Positive Planes Layer 4 TO Plane Obstructs Layer 4

No Hazards.

Positive Planes Layer 4 TO Via Pads Layer 4

No Hazards.

Positive Planes Layer 4 TO Via Holes Layer 4

No Hazards.

Total Hazards Found : 0

Non-Net Class Element To Element Clearances And Rules

-----------------------------------------------------

Route Border TO Via Pads Layer 1 Clearance: 0mm

No Hazards.

Route Border TO Traces Layer 1 Clearance: 0mm

No Hazards.

Part Pads SMD Layer 1 TO Route Border Clearance: 0mm

No Hazards.

Part Pads Thru Layer 1 TO Route Border Clearance: 0mm

No Hazards.

Board Outline TO Part Pads Thru Layer 1 Clearance: 0mm

No Hazards.

Board Outline TO Via Holes Layer 1 Clearance: 0mm

No Hazards.

Board Outline TO Via Pads Layer 1 Clearance: 0mm

No Hazards.

Board Outline TO Part Holes Layer 1 Clearance: 0mm

No Hazards.

Board Outline TO Placement Outlines Layer 1 Clearance: 0.25mm

No Hazards.

Board Outline TO Part Pads SMD Layer 1 Clearance: 0mm

No Hazards.

Board Outline TO Traces Layer 1 Clearance: 0mm

No Hazards.

Route Border TO Via Pads Layer 2 Clearance: 0mm

No Hazards.

Part Pads Thru Layer 2 TO Route Border Clearance: 0mm

No Hazards.

Board Outline TO Part Pads Thru Layer 2 Clearance: 0mm

No Hazards.

Board Outline TO Via Holes Layer 2 Clearance: 0mm

No Hazards.

Board Outline TO Via Pads Layer 2 Clearance: 0mm

No Hazards.

Board Outline TO Part Holes Layer 2 Clearance: 0mm

No Hazards.

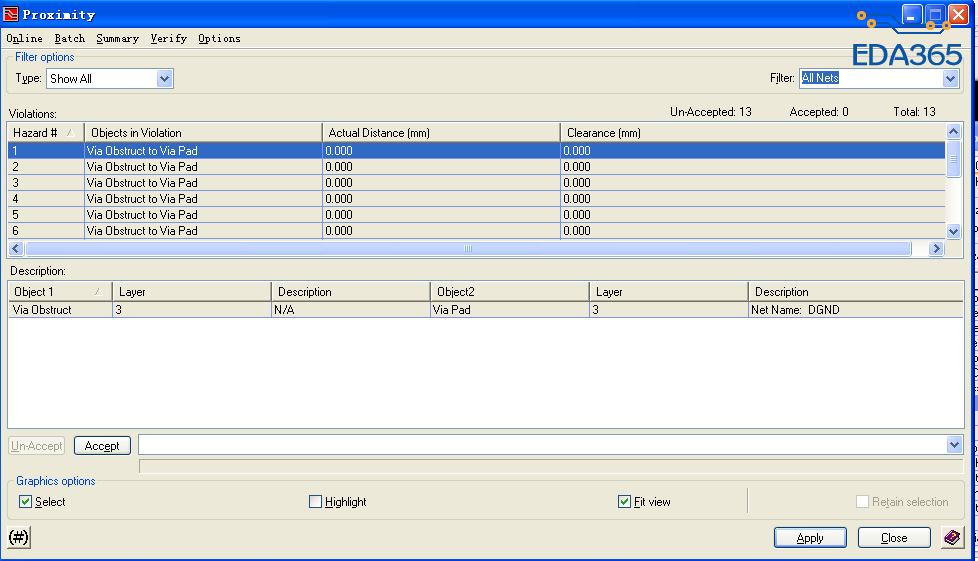

>> Via Obstructs Layer 3 TO Via Pads Layer 3 Clearance: 0mm

Hazards Found : 6

>> Via Holes Layer 3 TO Via Obstructs Layer 3 Clearance: 0mm

Hazards Found : 6

>> Traces Layer 3 TO Trace Obstructs Layer 3 Clearance: 0mm

Hazards Found : 1

Route Border TO Via Pads Layer 3 Clearance: 0mm

No Hazards.

Route Border TO Traces Layer 3 Clearance: 0mm

No Hazards.

Part Pads Thru Layer 3 TO Route Border Clearance: 0mm

No Hazards.

Board Outline TO Part Pads Thru Layer 3 Clearance: 0mm

No Hazards.

Board Outline TO Via Holes Layer 3 Clearance: 0mm

No Hazards.

Board Outline TO Via Pads Layer 3 Clearance: 0mm

No Hazards.

Board Outline TO Part Holes Layer 3 Clearance: 0mm

No Hazards.

Board Outline TO Traces Layer 3 Clearance: 0mm

No Hazards.

Route Border TO Via Pads Layer 4 Clearance: 0mm

No Hazards.

Route Border TO Traces Layer 4 Clearance: 0mm

No Hazards.

Part Pads SMD Layer 4 TO Route Border Clearance: 0mm

No Hazards.

Part Pads Thru Layer 4 TO Route Border Clearance: 0mm

No Hazards.

Board Outline TO Part Pads Thru Layer 4 Clearance: 0mm

No Hazards.

Board Outline TO Via Holes Layer 4 Clearance: 0mm

No Hazards.

Board Outline TO Via Pads Layer 4 Clearance: 0mm

No Hazards.

Board Outline TO Part Holes Layer 4 Clearance: 0mm

No Hazards.

Board Outline TO Placement Outlines Layer 4 Clearance: 0.25mm

No Hazards.

Board Outline TO Part Pads SMD Layer 4 Clearance: 0mm

No Hazards.

Board Outline TO Traces Layer 4 Clearance: 0mm

No Hazards.

Total Hazards Found : 13

Total Proximity Hazards Found : 13

----------------------------

CONNECTIVITY & SPECIAL RULES

----------------------------

Check For Unplaced Parts : YES

No Hazards.

Check For Missing Parts : YES

No Hazards.

Check EP Component Hazards : YES

No Hazards.

Check Trace Hangers : YES

No Hazards.

Check Trace Loops : YES

No Hazards.

Check Trace Widths : YES

No Hazards.

Check Single Point Nets : NO

Check NonPlane Unrouted/Partially Routed Nets : YES

No Hazards.

Check Plane Unrouted/Partial Routed Nets : YES

No Hazards.

Check Routed Plane Pins : YES

No Hazards.

Check Plane Islands : YES

No Hazards.

Check Dangling Vias/Jumpers : YES

No Hazards.

Check Unrouted Pins : YES

No Hazards.

Check Routed Non-Plated Pins : YES

No Hazards.

Check Minimum Annular Ring : NO

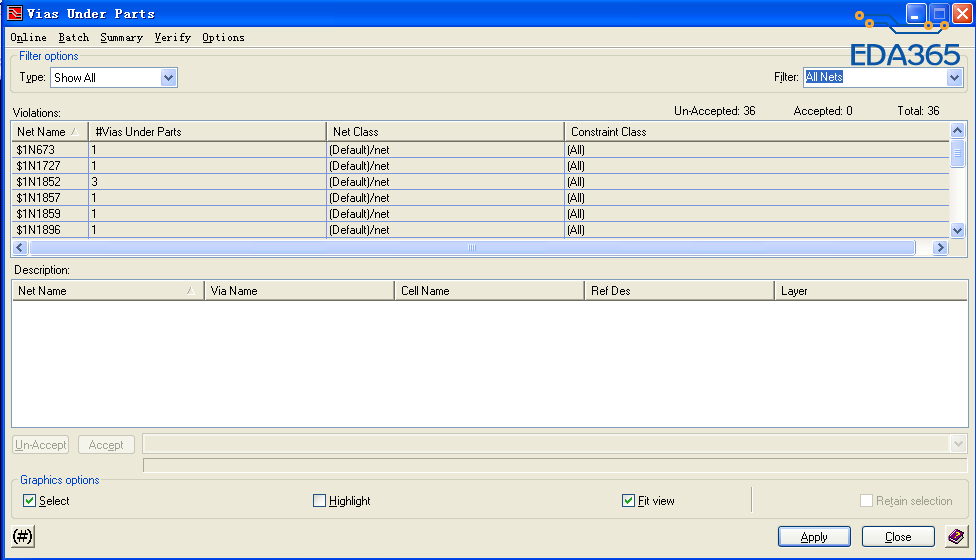

Check For Vias Under SMD Pads : YES

No Hazards.

Check For Vias Under Top Place Outlines : YES

Hazards Found : 25

Check For Vias Under Bottom Place Outlines : YES

Hazards Found : 11

Check For Missing Conductive Pads : NO

Check For Missing Part Soldermask Pads : NO

Check For Missing Via Soldermask Pads : NO

Check For Missing Solderpaste Pads : NO

Total Connectivity/SpecialRules Hazards Found : 36

====================================================================

Total DRC Hazards Found : 49

04:46 PM Thursday, April 16, 2015

ИпЪжАяУІПДПДетИіDRCЪЧЗёгаЪВУДЮЪЬт? ЮвПДАхПЈЩЯУЛгДЮЪЬтАЁЁЃ ЕЋЪЧdrcБЈИцга49ДІОЏИцЃЁ

ФувЊШЅевдѕУДЖЈЮЛУПвЛИіDRCГхЭЛЕФЮЛжУЃЌздМКвЛИіИіШЅевЃЌетИіБЈИцУЛгУЕФ

batch drc жЎКѓгжhazard viewЃЌРяУц#ЫЂаТвЛЯТСЫвЛИіИіВщ

вбОПДВЛЕНгаАзЩЋЕФОЏИцЯпСЫЁЃ ЕЋЪЧЛЙЪЧЬсЪОга49ДІ hanzards ЁЃ

ЮЪЬтдкетРяЁЃ ВЛжЊЕРЪЧЪВУДвтЫМЃЁ

ФуетСНИіЕиЗНаДЕФКмЧхГўСЫЁЃЕквЛИіЪЧМфОрДэЮѓЃЌОЭЪЧвЛИіНаVIA OBSTRUCTЕФЧјгђКЭФуЕФVIAППЬЋНќСЫЃЌОпЬхдкФФРявЊФуздМКвЛИіИіШЅЕуЛїВщПДЃЌПДVIA OBSTRUCTдкФФРяЁЃ

ЕкЖўИіЪЧVIA UNDER PARTSЮЪЬтЃЌОЭЪЧФуЩшжУСЫЦїМўЯТУцВЛФмДђПзЃЌетИіЮЅЗДЙцдђСЫЃЌОпЬхдкФФРяЩшвЊздМКШЅеввЛевЁЃ

СэЭтЮвЯыЫЕЃЌЕкЖўИіЙцдђЦфЪЕУЛБивЊШЅаоИФЃЌЮЅЗДОЭЮЅЗДСЫЃЌФуПЩвдбЁдёНгЪмЃЌОЭЪЧacceptЃЌУЛгаФЧУДЭъУРЕФDRCЃЌетИіКЭЦфЫћШэМўгаЧјБ№ЃЌЮвУЧгаЪБКђГіАхМИЧЇИіDRCЃЌЕЋЪЧжЛвЊжиЕуЕФУЛгаЮЅЗДЃЌЦфгрЕФwarnningОЭAcceptСЫЃЌЕБШЛФуЕУжЊЕРЪЧAcceptЕФЪЧЪВУДЁЃ

ФуПДВЛЕНDRCжИЪОЪЧвђЮЊФузѓБпАбФЧаЉЯдЪОЕФЙДШЅЕєСЫЁЃ