版主和其他高手帮忙看下,做cell库时遇到的几个不明白的地方

时间:10-02

整理:3721RD

点击:

一般做cell的顺序是:pads--holes--padstacks--cell

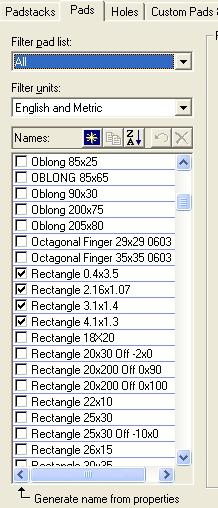

1.做pads是最简单的,也不会碰上问题,唯一不理解的地方是为什么有的小框勾上了,而有的没有,勾上的代表什么含义?刚开始我以为没有勾上在做padstacks是就不能选用,但是试验后发觉也是可以使用的。后来注意到最下面的Generate name from properties,这个name是用在哪里的?不是每个pads都会默认产生名字的么?这个properties又是哪个的properties?cell的?

-------------------------------------------------------------------------------------------------------------------------------------------

2.做holes时,type有两种选择,一种是dilled,另一种是punched,从表面上看,这两个都是打孔的意思,但是在这里肯定有着不同的意思,他们之间的区别是什么?在type选项的下方,有这个plated选项,他的表面意思是“镀金”,是否不勾上就意味着这个孔不会被镀铜,也就没有电气连接了?对于那些mounting hole是否就可以不勾上?而对于那些DIP封装上需要用到的hole,一定就要勾上plated?

----------------------------------------------------------------------------------------------------------------------------------------------

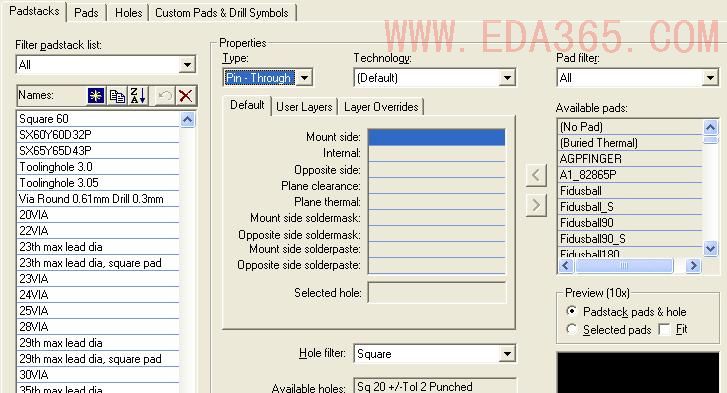

3.做padstacks时,困惑的就是有点不知道该选用哪些层。

譬如说:对于Pin-Though类型的padstacks,一共有以下可以使用的层:

mount side

internal

opposite side

plane clearance

plane thermal

mount side soldermask

opposite side soldermask

mount side solderpaste

opposite side solderpaste

不考虑soldermask和solderpaste,这两个很好搞定。mount side和opposite side也比较容易确定,但是对于internal side,该怎么确定呢?这个好像可以跟mount side一样,也可以不一样。这个确定的原则是什么呢?internal side是不是表示pin在内部走线层的状态?不管在布PCB时使用的是几层板,所有的内部走线层都死使用pin在这层的设置?而internal side跟mount side和opposite side的大小关系该怎么确定呢?

对于plane clearance和plane thermal,说得是pin在电源层的状态。plane clearance是pin在电源层跟电源层没有电气连接,而plane thermal是有电气连接时的连接方式。但是,如果做padstacks时不选用这两层,通过规则的设置应该也是可以达到这样的效果的吧?那这样设置的优点是什么呢?

[ 本帖最后由 lofeng 于 2008-7-13 11:13 编辑 ]

1.做pads是最简单的,也不会碰上问题,唯一不理解的地方是为什么有的小框勾上了,而有的没有,勾上的代表什么含义?刚开始我以为没有勾上在做padstacks是就不能选用,但是试验后发觉也是可以使用的。后来注意到最下面的Generate name from properties,这个name是用在哪里的?不是每个pads都会默认产生名字的么?这个properties又是哪个的properties?cell的?

-------------------------------------------------------------------------------------------------------------------------------------------

2.做holes时,type有两种选择,一种是dilled,另一种是punched,从表面上看,这两个都是打孔的意思,但是在这里肯定有着不同的意思,他们之间的区别是什么?在type选项的下方,有这个plated选项,他的表面意思是“镀金”,是否不勾上就意味着这个孔不会被镀铜,也就没有电气连接了?对于那些mounting hole是否就可以不勾上?而对于那些DIP封装上需要用到的hole,一定就要勾上plated?

----------------------------------------------------------------------------------------------------------------------------------------------

3.做padstacks时,困惑的就是有点不知道该选用哪些层。

譬如说:对于Pin-Though类型的padstacks,一共有以下可以使用的层:

mount side

internal

opposite side

plane clearance

plane thermal

mount side soldermask

opposite side soldermask

mount side solderpaste

opposite side solderpaste

不考虑soldermask和solderpaste,这两个很好搞定。mount side和opposite side也比较容易确定,但是对于internal side,该怎么确定呢?这个好像可以跟mount side一样,也可以不一样。这个确定的原则是什么呢?internal side是不是表示pin在内部走线层的状态?不管在布PCB时使用的是几层板,所有的内部走线层都死使用pin在这层的设置?而internal side跟mount side和opposite side的大小关系该怎么确定呢?

对于plane clearance和plane thermal,说得是pin在电源层的状态。plane clearance是pin在电源层跟电源层没有电气连接,而plane thermal是有电气连接时的连接方式。但是,如果做padstacks时不选用这两层,通过规则的设置应该也是可以达到这样的效果的吧?那这样设置的优点是什么呢?

[ 本帖最后由 lofeng 于 2008-7-13 11:13 编辑 ]

建议你在PADS里面做好转进来

这是一个可以解决cell问题的方法 在转换时有哪些注意事项呢?

但是这些问题。 呵呵