请教DxDesigner如何输出allegro的net list?

谢谢。

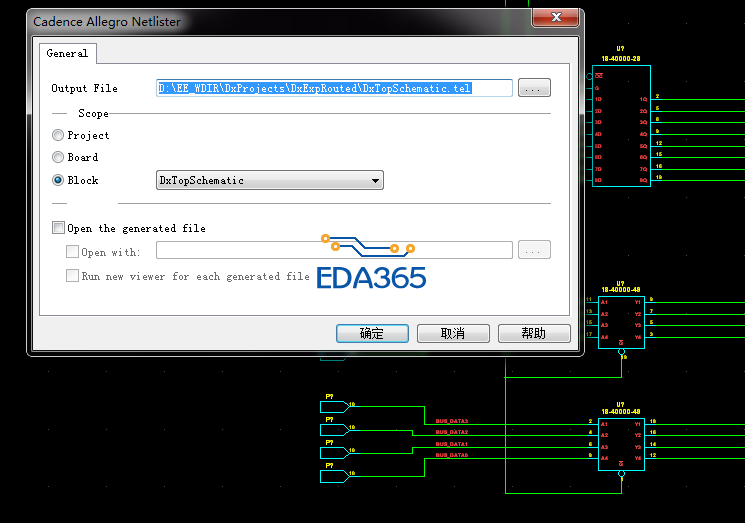

直接导出就可以了呀,里面有ALLEGRO的网表输出的,是TEL后缀的

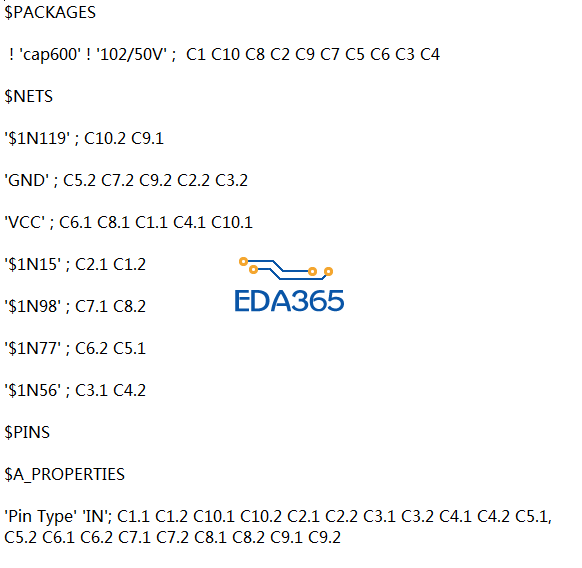

我输出的netlsit内容很少,有很多信息没有,请帮忙看看是什么原因呢?

$PACKAGES

! '' ; ?

$A_PROPERTIES

'PKG_TYPE' '0402'; ?

'VALUE' '50'; ?

$NETS

$PINS

哈,这是PCBBBS PROTEL版的小编摸,,,

是啊,小的不才,刚刚开始学dxdesinger,还望赐教

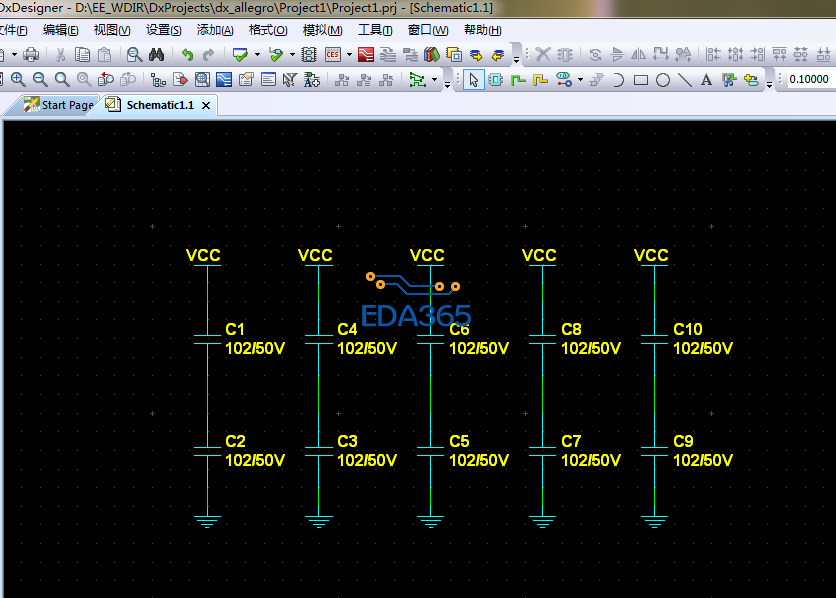

输出少什么信息,不会吧。我测试过用DX输出allegro的网表。用allegro导入没有任何问题。

测试如下。

那样DxDesigner怎样和allegro交互布局呢?

交互方面可以么?

应该要写个什么脚本程序吧,华为就是用DxD做SCH Allegro做PCB的

需要配置什么脚本文件吗?

这个问题我曾经花了几天时间研究,可以用了。最好用create netlist ,这个还可以检查原路图的一些问题,比如没有添加pkg_type。用export没这么多意提示,要是缺失属性导入到allegro会有问题

楼上哥们能详细介绍下方法吗?

没有哥们分享啊,哎.........

这位大哥。能详细介绍下吗。怎样使用DXDESIGNER 的原理图和allegro配。

现在设计电路少了,不太常过来了。

不知道大家的问题出在什么地方,因为我对allegro不熟,以前用mentor cdb流程比较多,后来因为需要,将 dx 添加属性,走了网表流程到allegro下。当时用的版本是ee2005.

需要在原理图符号中具有device,part,ref des,pkg_type 4个属性(level有书写也需要,实际测试貌似可以不用),就可以生成网表导入到allegro,导出时尽量用pcb interface(tools菜单),不容易出问题。

另:刚刚在ee vx.1与spb 16.6测试,成功,只不过2007后mentor恢复了使用part number而非device作为器件的主要标识符,但若走该流程,device看来还得添上。至少vx.1是这个样子的

看下下面我的回复是否可解决您的问题

我没有所谓的"Dx to Allegro Op SW"来霉素设计转化为Allegro网络表的特别许可证。请帮助,让我知道有没有什么技巧或任何其他方式来从DxDesigner中快板的网表