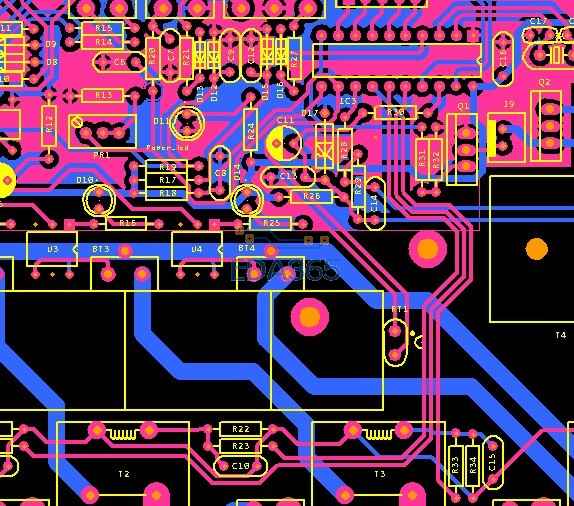

Expedition 黄色的飞线肿么回事,看图

不知怎么出来的,拉了线了,知道的解答下。

把左边Ordered&Routed Netlines那个√关了就行了。

谢谢解答,我知道关了那个就可以了,问题是,别的网线不用关也没有呀,你那是治标不是治本呀。

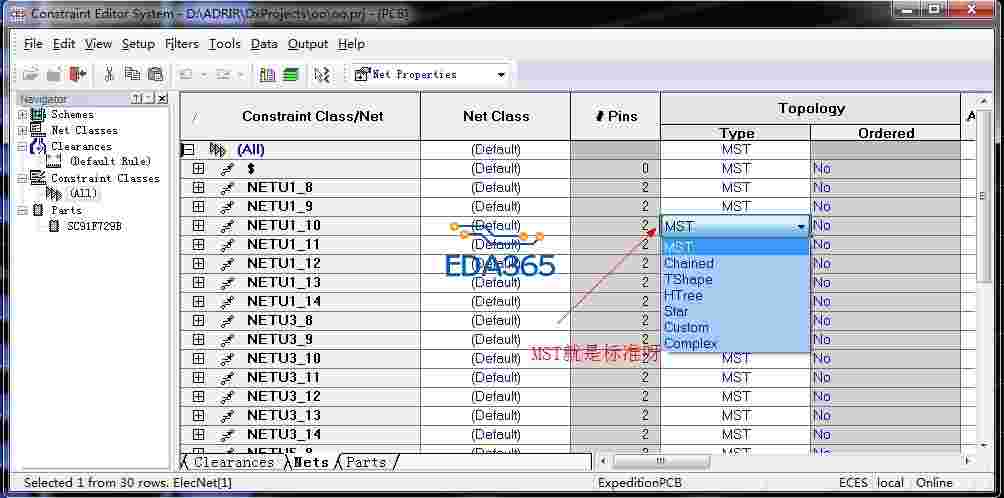

已经解决了,是那个网络定义了拓扑的原因,恢复标准就可以了。

你说的那个拓扑是不是在CES里面设置的那个拓扑结构啊?我学习mentor时间不长,还请多多指教。有的时候拓扑设置的不对的话线连不上的,前几天还出现过这个情况。

是的,是CES里面那个拓扑结构。我学习几年了还未入门呢。

对了,顺便问一下,CES可以不关闭的情况下,规则起作用吗?比如在CES修改一下铺铜间距,又点了更新所有。看PCB的铜没变化。关了CES才起作用。感觉很麻烦。

有的可以有的不能吧,等长什么的那些可以,然后拓扑那些也可以,如果更改了然后更新所有都不行的话那就必须得关了。我一般是几个人合作的,不关的话别人没法用啊呵呵。

兄弟如何恢复标准,我折腾半天没有恢复呀,求解!谢谢!

进入CES,将你定义了拓扑的网络定义成MST,就可以了。

这样不行的呀!因为后面是ordered属性,没法修改成MST呀

你那可以修改是因为ordered属性是NO,我现在是yes呀!

ordered属性是YES肿么不可以呢,你看图。

这个飞线是可以存在的,它表明此线是进行了拓扑规划并完成布线的(ordered and routed netlines),如果删掉完成的布线,则飞线的颜色会变成粉色(ordered and opened netlines)。

当网络不是MST时,表明此网络是设计者进行规划的Ordered,则此飞线会出现,起到提示作用,没有其它影响。

CES不用关掉也可以更新PCB,只需要点击右下角3个小灯最右边的就可以更新了,当CES设置变化时,此灯会变成黄色,点击后变成绿色表明CES和PCB同步!

谢谢楼上,看得出您是高手,说得比较详细,那个不用关闭CES也能更新的问题我已经解决了,一次无意中看外国的DEMO看到了这样的操作,

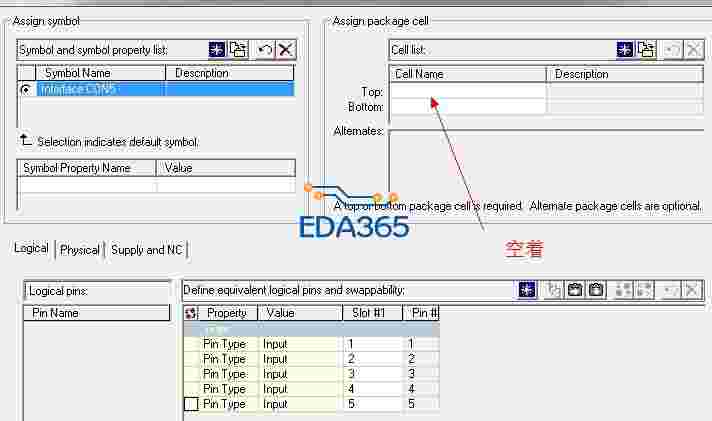

可以先不做Cell(空着),但是是要建Part的,因为Part才代表了元器件,不同的器件用不同的Part Number代表,生成器件清单也是以此为依据的。Sym不能代表器件,例如电阻电容类器件,有很多种,原理图中可以用同一个Sym。

EE7.X后我基本山就不用Netlist流程了。

我用的是2005版本,修改的时候就没有提示窗口弹出来,后来我将那些不能修改的重新建constraint classes后现在就能修改了。非常感谢!

灰常灰常感谢你,你说的方法,我试了一下,的确如此,画原理图用PART,CELL先不弄,这样就差不多达到效果了。

现在EE整个流程就基本顺了。原理图,编号出清单,出PCB,出光绘。

说句题外话,其实DX挺好用的,很多人说不美观,换一下字体及大小,就很漂亮了,

功能上还是很强的,如一条线插入元件直接插入就可以了。还有元件或者属性NET复制,很智能

不明白你说的:可以先不做Cell(空着)...

能说详细些!

请教下,2005版本上没有看到右下角有灯呀,怎么设置才有?

我想就是PCB的封装不用建,先画你的原理图就了,出BOM之类的都不会影响.

?

你创建的PDB(pat number)有没有关联CELL?不然在Expedition中如何DO?

这种就是先不管PCB只管原理图的做法,要做PCB的时候还是得画上cell的。

li_suny 已经说得很明白了呀。先不做CELL的意思是,只有SYM+PART就可以画原理图,编号,出清单了。

要做PCB设计时,当然要加上CELL了。

右下角DRC处有几个灯的呀,很小的,

可以这样理解:

1.建Symbol时,不指定PKG_TYPE

2.在建Part numger关联CELL

DX-EXP Flow可以这样理解:

1.建Symbol时,不指定PKG_TYPE

2.在建Part numger关联CELL

?

2007版本的我看到有,2005版本没有看到有。

SYM貌似神马都不指定都是可以的,

不过我一般指定编号,元件值,以及PDB名,前2个显示,后者隐藏,就可以了。

Dx-Exp. 创建Part numger时关联CELL?

想关联就关联,不想就不关联,

前面讨论的不关联的意思是,有时候做原理图,不一定要先做CELL。

就是创建Part的时候Cell栏可以先空着,这样无法做PCB,但不影响原理图设计和Package等操作。

是的,还可以通过Part创建Cell,对BGA类器件有一些方便之处,可以不用手工输入A,B,C...,因为目前Exp还没有BGA Wizard。

2005没有这几个小灯,但CES和PCB的同步更新可以通过在CES保存设置来实现,而到了EE7.x,CES就没有保存按钮了,关闭CES自动保存,然后同步到PCB,这样操作起来比较麻烦,所以就通过这个灯来同步。

明白了,谢谢!

大侠,请教几个问题:

1.在CPU里面的电源引脚我想多个引脚共用一个VIA过孔,怎么设置?如图,有的时候网络可以两个共用,有的共用后VIA过孔就没有了?

2.差分线怎么会开来走线?

1.最简单的方法就是把过孔先锁定,然后就不会被自动优化掉。

2.步骤如下:1)不选择任何网络前提下,点击F3进入布线状态,2)按住ALT键,3)选择网络进行布线。

这样,差分对可分开布线。

谢谢!那如果我要把元件与走线一起移动有办法吗?