AD采集,UDP传输

补充内容 (2017-8-30 15:30):

连续不停采集的数据能利用verilog编写的UDP协议传上labview而不漏包吗?总是感觉理论可行,但实际上就有问题!

补充内容 (2017-8-31 15:15):

我使用两个fifo交替存储,存到一定数据,才开始传输,写的频率远小于读的频率。理论上是不会有溢出情况的。但后来发现,程序运行过程中,有时该读取fifo数据,但并没有读出。可是条件成立,读使能,也有数据。它为什么不正确运行?

PFGA资源够的话,把FIFO深度设置为超过4000,或者生成一个比如8000byte深度的rom,将rom里面的数据读取出来用labview显示,看有没有丢数据;

或者调试一下,改用串口打印数据,看有没有丢数据;

网络也要分包的啊!

我一次传输512字节,因为labview最大一次接收548字节

fifo的存储深度是多少,有可能是存储数据满了导致丢数

fifo的深度设置4K,1K,512都试过,没影响。我是用的两个fifo交替存储,写fifo的频率降低,也没有用。理论上是不会溢出的。

”如果从ROM中连续写入fifo,labview接收数据就是正确的“,这个是测试过的么,那检测一下AD采集端,采集端有没有可能丢数据。

”signal tapii 里观察数据无丢失“,是fifo读出的数据没有丢失么

确认一下fifo读取的是没有数据,还是读取的数据就是0x00

后来发现,读ROM也是有问题的,和AD同样的问题。

我一直采数据,两个fifo交替存储,一个fifo存够数据后,才一次性读空,并传输。写fifo的频率很慢,如果正常运行是不会溢出的。

后来发现,程序有时并没有正常运行,条件到了,本应该读数了,但它读了一个就过了。

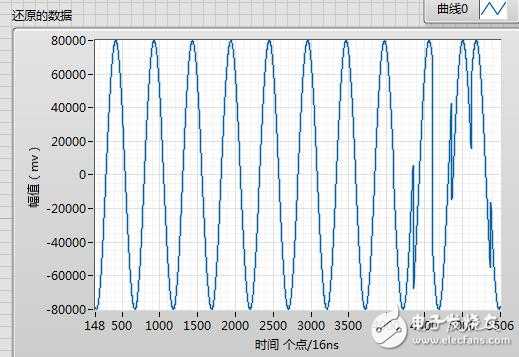

感觉像时序错乱了。labview里的结果就是4K个点后数据错乱。如果时序约束没约束好,会有这种错误吗?

可以给写fifo设置一个深度,例如fifo1写满100个字节,就切换到fifo2,然后开始读fifo1,读满100个字节或者读空为止;

”程序有时并没有正常运行,条件到了,本应该读数了,但它读了一个就过了“,是读了一个字节就退出了么,如果是低速的话,时序一般还好,可以看下时序报告,然后检查一下读fifo这一块的逻辑

fifo的读写就是你说的这样的;

有时是读了一个字节就退出了,

写频率是20M左右,读是62.5M。

时序报告是有问题的

这个。时钟速率不高啊,警告还这么多,时序警告好像有点严重,fifo读写这一块写的很复杂么,优化一下吧;

可以用signaltap看一下读fifo异常退出时的情况,抓几个关键信号看下

现在看signal tapii已经没有异常,fifo的写、读也换了好几种方式,理论分析都没什么问题。但是labview始终是在4K个点后异常,想不通啊。

FIFO深度最大只能设置为4K

发现一个问题,读空后,signal tap ii看到fifo输出不为0,为最后一个读出的数据;若读空后,异步清零,输出为另一个数据,但仍然不为0.

补充内容 (2017-9-11 21:40):

查了下资料,好像cyclone4的fifo的异步清零,只能清标志

我有的点懵,好像应该是Labview的问题,此问题依然没有解决!