fpga应用篇(二):边沿检测

时间:10-02

整理:3721RD

点击:

fpga应用篇(二):边沿检测

上一篇介绍了阻塞赋值与非阻塞赋值,这次我们利用非阻塞赋值产生一个简单的应用即边沿检测,边沿检测一般用来产生使能信号。

程序如下:

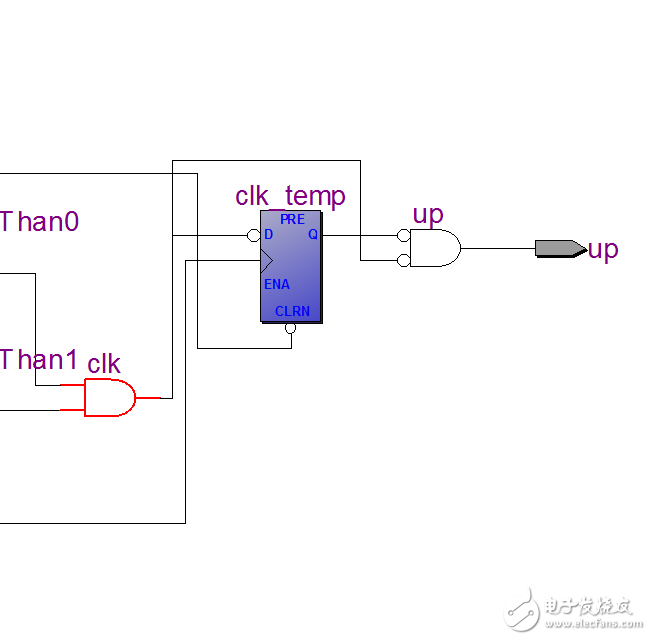

综合后电路:

clk为主时钟分频之后得到的,程序中定义了clk_temp;我们希望clk_temp比clk差一个主时钟的宽度,从综合后的电路我们可以看出,clk经过一个触发器之后生成clk_temp;符合我们的要求。

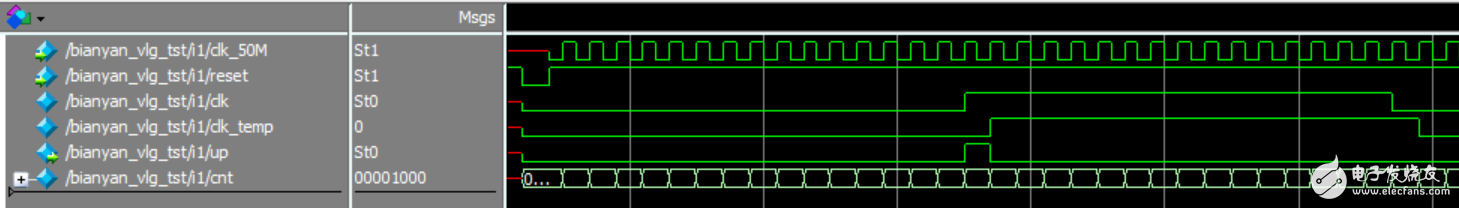

从仿真结果来看,clk_temp为clk延迟一个主时钟的宽度,可以看出,在clk上升沿有一个和主时钟宽度一致的up信号,即完成上升沿检测。同理,下降沿检测一个道理,只需在源程序中改动一个符号的位置,你知道么?欢迎留言。

推荐一个公众号:FPGA干货,每天都推送有关fpga的内容

赞!