CPLD数字滤波

时间:10-02

整理:3721RD

点击:

若输入信号电平在至少3个连续的时钟周期保持为1或0不变?

怎么理解 这个都看不懂 求指教

怎么理解 这个都看不懂 求指教

论文为 用FPGA实现的正交解码/计数器

小白在学习CPLD,需要做一个脉冲计数,脉冲形式有正交,CW,CCW 方向加脉冲形式,

各位大神有没有什么好的方案 推荐啊

跪求

额,3个连续1或者3个连续0就满足条件!这还怎么解释啊!

程序不知道咋编写的

程序不知道咋编写的、能提供点思路吗?

将输入信号输入到移位寄存器中,然后从中取连续的三个寄存器,用F=ABC+ ?A ?B ?C进行判断是否为逻辑1或0

楼上正解

楼上正解

论文上的方案感觉复杂很多,就是不知道怎么实现他

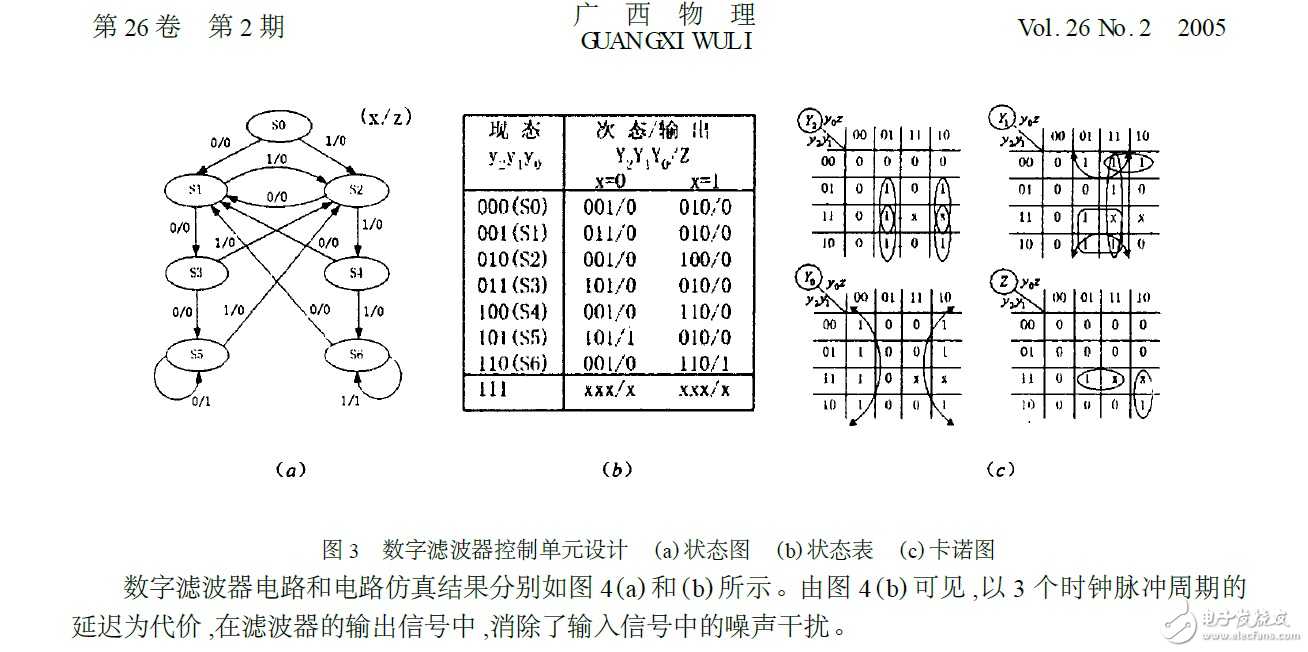

如图

论文上的方案感觉复杂很多,就是不知道怎么实现他

状态机的使用,三个寄存器表示一个输入信号在三个连续时钟周期的逻辑状态,而x代表紧接的输入信号电平,而A表征这个x电平和其相邻的两个电平是否满足全1或全0逻辑结果。对于你给的图片我理解不透