fpga计数延时该如何实现

时间:10-02

整理:3721RD

点击:

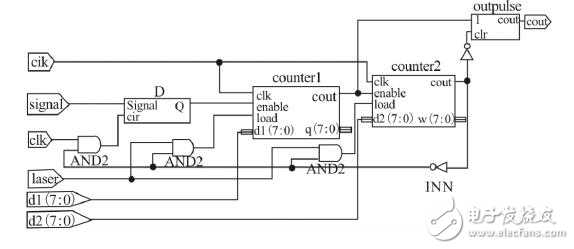

小白求问下,如图这种的计数延时,里面的计数器,D触发器,门在编写时有相应的模块么?还是只能用语言写

补充内容 (2017-1-7 16:40):

左上角也是clk,signal是脉冲信号,D模块接收时钟与signal,counter模块是减计数模块,想要实现的功能是两个8为计数器置分别置数是d1,d2,当触发信号signal到达,触发D模块,产生使能信号enable启动counter1,此时cout1为低电平,counter2的使能端被cout1输出的低电平封锁不计数。当counter1减到0,counter1溢出,输出为cout1为高电平,启动counter2计数同时使outpulse模块产生高电平信号。当counter2减到0,输出cout2为高电平,使outpulse复位,同时cout2通过一个反向器分别于D触发器的清零端,counter1,counter2置数端相与,使D触发器清零,将d1,d2的数重新置入,简单功能就是接受一个脉冲信号,在延时后在输出一个预设宽度的脉冲。

补充内容 (2017-1-7 16:40):

左上角也是clk,signal是脉冲信号,D模块接收时钟与signal,counter模块是减计数模块,想要实现的功能是两个8为计数器置分别置数是d1,d2,当触发信号signal到达,触发D模块,产生使能信号enable启动counter1,此时cout1为低电平,counter2的使能端被cout1输出的低电平封锁不计数。当counter1减到0,counter1溢出,输出为cout1为高电平,启动counter2计数同时使outpulse模块产生高电平信号。当counter2减到0,输出cout2为高电平,使outpulse复位,同时cout2通过一个反向器分别于D触发器的清零端,counter1,counter2置数端相与,使D触发器清零,将d1,d2的数重新置入,简单功能就是接受一个脉冲信号,在延时后在输出一个预设宽度的脉冲。

你的需求是什么?

类似图中的该怎么编,想知道使用这种计数器有没有模块,一个系统里包含这种计数器该怎么编

类似图中的该怎么编,想知道使用这种计数器有没有模块,一个系统里包含这种计数器该怎么编

你是一定要用原理图输入么?写verilog多好,计数器延时随便找个教程看,一般前两课就会出现这个知识点,两三行就写出来了。

恩恩,初学这个,前面都在讲的是小模块比如d触发器,与非门什么的,想知道这原理图里的很多模块连接起来的这种如何用verilog编写,计数器verilog里面也需要自己编么?

你不能只给一个电路图,要说出里面每个小模块是代表什么,引脚是做什么的,这样才能让别人帮你弄。

比如clk一般是时钟,那么你的cik又是什么,通过分析只能猜测也是时钟,但这些逻辑不能靠别人猜,要你自己注明。还有就是count1输入的参数是什么,要实现什么目的,里面实现的可以是黑盒,大家帮你想,但是你连需求都不说,别人也不知道怎么帮你实现。最后就是最好下次发帖求助最好有积分奖励,虽然不值钱,毕竟也尊重一下回答问题人的劳动成果。

问题描述不明确,无法解答。。

用 Verilog 或者 VHDL 做设计输入,计数器很好写的;

reg [9:0] cnt;

always@(posege clk)

begin

if(rst)

cnt <= 0;

else if(cnt < 100)

cnt <= cnt + 1;

else

cnt <= 0;

end