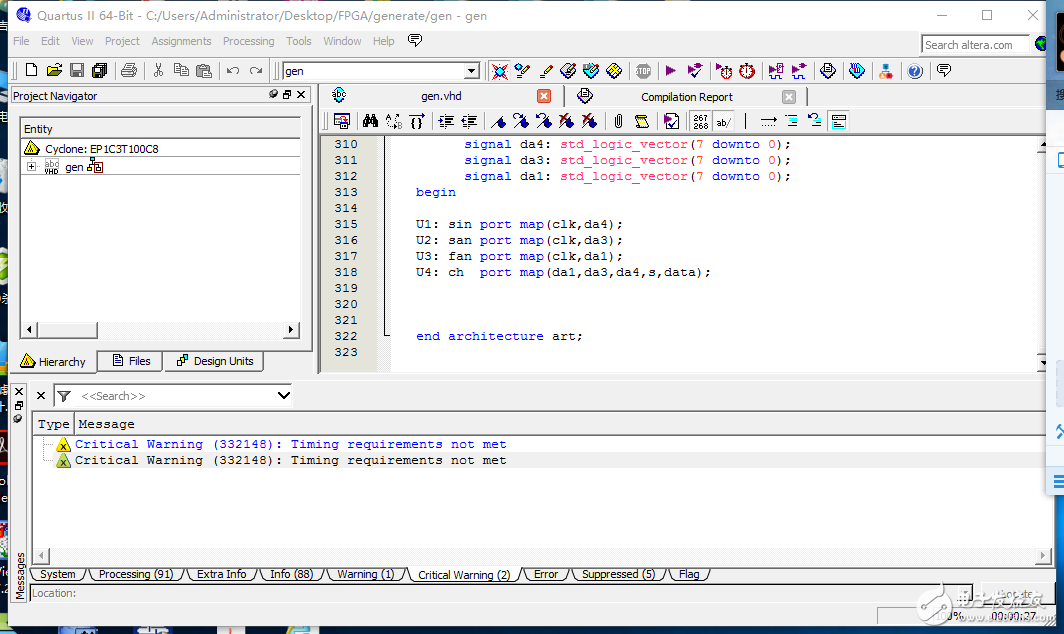

编译时出现 Critical Warning (332148): Timing requirements not met ,以及modelsim仿真时,时钟是未知信号

时间:10-02

整理:3721RD

点击:

刚开始学vhdl,想写一个波形发生器的代码,但过程中编译老是出现Critical Warning (332148): Timing requirements not met的警告,想用modelsim仿真,但是时钟也都是未知信号,想知道是和这个警告有关系吗?还是我的testbench写错了。之后用自己这个程序,把FPGA输出接到dac0832波形能正常输出方波正弦波以及三角波。以及突然发现不论是自己写的,还是网上直接复制粘贴的都有这个警告:Critical Warning (332148): Timing requirements not met,这又是为何呢?本人真真是萌新中的萌新啊~学了几天懂得也不多,就是按网上的代码改改~求各位前辈指点指点~积分什么的各路大神也会太在意的吧~~~(只有2个哭~)

以下是代码:

----------------------------------------------------

--正弦波

--

----------------------------------------------------

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity sin is

port(clk_sin:in std_logic;

--reset:in std_logic;

dd4:out std_logic_vector(7 downto 0));--———输出范围为0到255

end;

architecture dacc of sin is

signal q: integer range 63 downto 0;

signal clk4:std_logic;

begin

lcd_clk:

process(clk_sin)

variable count:integer range 0 to 50000000;

variable clk1:std_logic;

begin

-- if reset='0'then

-- count:=0;

--els

if(clk_sin'event and clk_sin='1')then --rising_edge(clk)

--if(count="100110001001011001111111")then

--count '0');

if(count=24000)then

count:=0;

clk1:=not clk1;

else count:=count+1;

end if;

end if;

clk4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 null;

end case;

end process;

end architecture dacc;

----------------------------------------------------

--三角波

--

----------------------------------------------------

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity san is

port(clk_san:in std_logic;

--reset:in std_logic;

dd3:out std_logic_vector(7 downto 0));

end san;

architecture art of san is

signal b:std_logic;

signal clk3:std_logic;

signal c:std_logic_vector(7 downto 0);

begin

lcd_clk:

process(clk_san)

variable count:integer range 0 to 50000000;

variable clk1:std_logic;

begin

-- if reset='0'then

-- count:=0;

--els

if(clk_san'event and clk_san='1')then --rising_edge(clk)

--if(count="100110001001011001111111")then

--count '0');

if(count=24000/8)then

count:=0;

clk1:=not clk1;

else count:=count+1;

end if;

end if;

clk3 '0');

if(count=2400*32)then

count:=0;

clk0:=not clk0;

else count:=count+1;

end if;

end if;

clk1 dd1 dd1 null;

end case;

end process;

end architecture;

-------------------------------------------------------

--波形选择

--

--------------------------------------------------------

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity ch is

port(cdd1,cdd3,cdd4 : in std_logic_vector (7 downto 0);

s: in std_logic_vector(1 downto 0);

y: out std_logic_vector (7 downto 0));

end entity ch;

architecture art of ch is

begin

process(s,cdd1,cdd3,cdd4)

begin

case s is

when "00"=>y y y y null;

end case;

end process;

end architecture art;

--------------------------------------------------------

--主模块

--

--------------------------------------------------------

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity gen is

port(clk:in std_logic;

data :out std_logic_vector(7 downto 0);

s:in std_logic_vector(1 downto 0));

end gen;

architecture art of gen is

component sin

port(clk_sin:in std_logic;

dd4:out std_logic_vector(7 downto 0));

end component;

component san

port(clk_san:in std_logic;

dd3:out std_logic_vector(7 downto 0));

end component;

component fan

port(

clk_fan : in std_logic;

dd1 : out std_logic_vector(7 downto 0));

end component;

component ch

port(cdd1,cdd3,cdd4 : in std_logic_vector (7 downto 0);

s: in std_logic_vector(1 downto 0);

y: out std_logic_vector (7 downto 0));

end component;

-- component f

-- port(clk : in std_logic;

--s: in std_logic_vector(1 downto 0);

--z1,z2,z3,z4: out std_logic);

-- end component;

--signal _clk:std_logic;

-- signal ch:std_logic_vector (1 downto 0);

signal da4: std_logic_vector(7 downto 0);

signal da3: std_logic_vector(7 downto 0);

signal da1: std_logic_vector(7 downto 0);

begin

U1: sin port map(clk,da4);

U2: san port map(clk,da3);

U3: fan port map(clk,da1);

U4: ch port map(da1,da3,da4,s,data);

end architecture art;

------------------------------------------------------------------------------

testbench代码 :

-- Copyright (C) 1991-2012 Altera Corporation

-- Your use of Altera Corporation's design tools, logic functions

-- and other software and tools, and its AMPP partner logic

-- functions, and any output files from any of the foregoing

-- (including device programming or simulation files), and any

-- associated documentation or information are expressly subject

-- to the terms and conditions of the Altera Program License

-- Subscription Agreement, Altera MegaCore Function License

-- Agreement, or other applicable license agreement, including,

-- without limitation, that your use is for the sole purpose of

-- programming logic devices manufactured by Altera and sold by

-- Altera or its authorized distributors. Please refer to the

-- applicable agreement for further details.

-- ***************************************************************************

-- This file contains a Vhdl test bench template that is freely editable to

-- suit user's needs .Comments are provided in each section to help the user

-- fill out necessary details.

-- ***************************************************************************

-- Generated on "12/10/2016 11:23:16"

-- Vhdl Test Bench template for design : gen

--

-- Simulation tool : ModelSim-Altera (VHDL)

--

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY gen_vhd_tst IS

END gen_vhd_tst;

ARCHITECTURE gen_arch OF gen_vhd_tst IS

-- constants

-- signals

SIGNAL clk : STD_LOGIC;

SIGNAL data : STD_LOGIC_VECTOR(7 DOWNTO 0);

SIGNAL s : STD_LOGIC_VECTOR(1 DOWNTO 0);

COMPONENT gen

PORT (

clk : IN STD_LOGIC;

data : OUT STD_LOGIC_VECTOR(7 DOWNTO 0);

s : IN STD_LOGIC_VECTOR(1 DOWNTO 0)

);

END COMPONENT;

constant clk_period :time :=20 ns;

BEGIN

i1 : gen

PORT MAP (

-- list connections between master ports and signals

clk => clk,

data => data,

s => s

);

init : PROCESS

-- variable declarations

BEGIN

s<="11";-- code that executes only once

WAIT;

END PROCESS init;

always : PROCESS

-- optional sensitivity list

-- ( )

-- variable declarations

BEGIN

wait for clk_period/2;

clk<='1';

wait for clk_period/2;

clk<='0'; -- code executes for every event on sensitivity list

WAIT;

END PROCESS always;

END gen_arch;

萌新求助~~~哇哇哇~

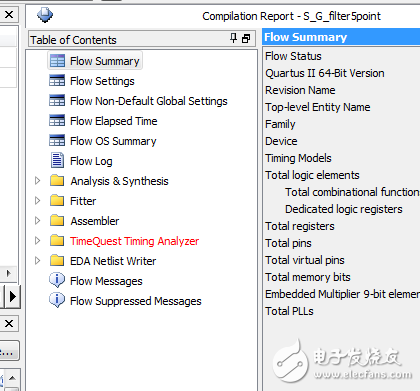

综合完了以后,Timequest Timing是红色的,时序约束怎么做去网上查查吧。要是功能没那么复杂,不做约束也行,就别管Timing requirements not met了。另外我看你的仿真波形,UUU表示,你都没给信号初值呢。在Testbench里要给用到的信号初值。比如这样:

init : PROCESS

-- variable declarations

BEGIN

-- code that executes only once

key1<='1'; --按键没有按下

addata<="01000110";

wait for 30_000 ns;

key1<='0';

wait for 30_000_000 ns;

key1<='1';

WAIT;

END PROCESS init;

我也刚搞FPGA没多久,片面看法,坐等大神回答。

以下是代码:

----------------------------------------------------

--正弦波

--

----------------------------------------------------

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity sin is

port(clk_sin:in std_logic;

--reset:in std_logic;

dd4:out std_logic_vector(7 downto 0));--———输出范围为0到255

end;

architecture dacc of sin is

signal q: integer range 63 downto 0;

signal clk4:std_logic;

begin

lcd_clk:

process(clk_sin)

variable count:integer range 0 to 50000000;

variable clk1:std_logic;

begin

-- if reset='0'then

-- count:=0;

--els

if(clk_sin'event and clk_sin='1')then --rising_edge(clk)

--if(count="100110001001011001111111")then

--count '0');

if(count=24000)then

count:=0;

clk1:=not clk1;

else count:=count+1;

end if;

end if;

clk4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 dd4 null;

end case;

end process;

end architecture dacc;

----------------------------------------------------

--三角波

--

----------------------------------------------------

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity san is

port(clk_san:in std_logic;

--reset:in std_logic;

dd3:out std_logic_vector(7 downto 0));

end san;

architecture art of san is

signal b:std_logic;

signal clk3:std_logic;

signal c:std_logic_vector(7 downto 0);

begin

lcd_clk:

process(clk_san)

variable count:integer range 0 to 50000000;

variable clk1:std_logic;

begin

-- if reset='0'then

-- count:=0;

--els

if(clk_san'event and clk_san='1')then --rising_edge(clk)

--if(count="100110001001011001111111")then

--count '0');

if(count=24000/8)then

count:=0;

clk1:=not clk1;

else count:=count+1;

end if;

end if;

clk3 '0');

if(count=2400*32)then

count:=0;

clk0:=not clk0;

else count:=count+1;

end if;

end if;

clk1 dd1 dd1 null;

end case;

end process;

end architecture;

-------------------------------------------------------

--波形选择

--

--------------------------------------------------------

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity ch is

port(cdd1,cdd3,cdd4 : in std_logic_vector (7 downto 0);

s: in std_logic_vector(1 downto 0);

y: out std_logic_vector (7 downto 0));

end entity ch;

architecture art of ch is

begin

process(s,cdd1,cdd3,cdd4)

begin

case s is

when "00"=>y y y y null;

end case;

end process;

end architecture art;

--------------------------------------------------------

--主模块

--

--------------------------------------------------------

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity gen is

port(clk:in std_logic;

data :out std_logic_vector(7 downto 0);

s:in std_logic_vector(1 downto 0));

end gen;

architecture art of gen is

component sin

port(clk_sin:in std_logic;

dd4:out std_logic_vector(7 downto 0));

end component;

component san

port(clk_san:in std_logic;

dd3:out std_logic_vector(7 downto 0));

end component;

component fan

port(

clk_fan : in std_logic;

dd1 : out std_logic_vector(7 downto 0));

end component;

component ch

port(cdd1,cdd3,cdd4 : in std_logic_vector (7 downto 0);

s: in std_logic_vector(1 downto 0);

y: out std_logic_vector (7 downto 0));

end component;

-- component f

-- port(clk : in std_logic;

--s: in std_logic_vector(1 downto 0);

--z1,z2,z3,z4: out std_logic);

-- end component;

--signal _clk:std_logic;

-- signal ch:std_logic_vector (1 downto 0);

signal da4: std_logic_vector(7 downto 0);

signal da3: std_logic_vector(7 downto 0);

signal da1: std_logic_vector(7 downto 0);

begin

U1: sin port map(clk,da4);

U2: san port map(clk,da3);

U3: fan port map(clk,da1);

U4: ch port map(da1,da3,da4,s,data);

end architecture art;

------------------------------------------------------------------------------

testbench代码 :

-- Copyright (C) 1991-2012 Altera Corporation

-- Your use of Altera Corporation's design tools, logic functions

-- and other software and tools, and its AMPP partner logic

-- functions, and any output files from any of the foregoing

-- (including device programming or simulation files), and any

-- associated documentation or information are expressly subject

-- to the terms and conditions of the Altera Program License

-- Subscription Agreement, Altera MegaCore Function License

-- Agreement, or other applicable license agreement, including,

-- without limitation, that your use is for the sole purpose of

-- programming logic devices manufactured by Altera and sold by

-- Altera or its authorized distributors. Please refer to the

-- applicable agreement for further details.

-- ***************************************************************************

-- This file contains a Vhdl test bench template that is freely editable to

-- suit user's needs .Comments are provided in each section to help the user

-- fill out necessary details.

-- ***************************************************************************

-- Generated on "12/10/2016 11:23:16"

-- Vhdl Test Bench template for design : gen

--

-- Simulation tool : ModelSim-Altera (VHDL)

--

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY gen_vhd_tst IS

END gen_vhd_tst;

ARCHITECTURE gen_arch OF gen_vhd_tst IS

-- constants

-- signals

SIGNAL clk : STD_LOGIC;

SIGNAL data : STD_LOGIC_VECTOR(7 DOWNTO 0);

SIGNAL s : STD_LOGIC_VECTOR(1 DOWNTO 0);

COMPONENT gen

PORT (

clk : IN STD_LOGIC;

data : OUT STD_LOGIC_VECTOR(7 DOWNTO 0);

s : IN STD_LOGIC_VECTOR(1 DOWNTO 0)

);

END COMPONENT;

constant clk_period :time :=20 ns;

BEGIN

i1 : gen

PORT MAP (

-- list connections between master ports and signals

clk => clk,

data => data,

s => s

);

init : PROCESS

-- variable declarations

BEGIN

s<="11";-- code that executes only once

WAIT;

END PROCESS init;

always : PROCESS

-- optional sensitivity list

-- ( )

-- variable declarations

BEGIN

wait for clk_period/2;

clk<='1';

wait for clk_period/2;

clk<='0'; -- code executes for every event on sensitivity list

WAIT;

END PROCESS always;

END gen_arch;

萌新求助~~~哇哇哇~

好久没看VHDL的代码了,有点看不懂。Timing requirements not met应该是没做时序约束导致的。

综合完了以后,Timequest Timing是红色的,时序约束怎么做去网上查查吧。要是功能没那么复杂,不做约束也行,就别管Timing requirements not met了。另外我看你的仿真波形,UUU表示,你都没给信号初值呢。在Testbench里要给用到的信号初值。比如这样:

init : PROCESS

-- variable declarations

BEGIN

-- code that executes only once

key1<='1'; --按键没有按下

addata<="01000110";

wait for 30_000 ns;

key1<='0';

wait for 30_000_000 ns;

key1<='1';

WAIT;

END PROCESS init;

我也刚搞FPGA没多久,片面看法,坐等大神回答。