Xilinx SelectMAP 配置问题

时间:10-02

整理:3721RD

点击:

想通过SelectMAP方式配置Xilinx Virtex II。Selectmap的时序通过另外一个Altera FPGA控制,配置数据存放在SRAM中,Altera FPGA读出SRAM数据,每来一个CCLK时钟,把数据加载到SelectMAP端口,现在一直通mcs文件配置到FPGA中,但是不成功,想问下几个问题:(1)配置文件是bit文件还是mcs文件或者是其他的文件?;(2)SelectMAP端口的CCLK配置时钟是随便自己定义的时钟么?(3)SelectMAP的D[0:7],D0是高位,D7是低位,那么配置时候mcs文件需要改变里面数据的高低位么?(4)大神告知一些配置时候细节,仿真看了时序自己觉得没问题。谢谢大家帮忙看看~

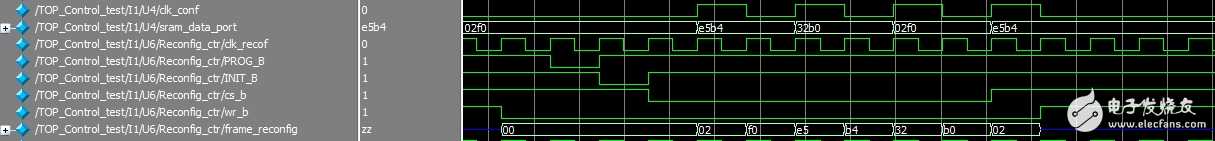

仿真图

frame_reconfig为SelectMAP数据端口D[0:7]

问题解决了,配置过程中初始化出错了,PROG_B拉低开始清空配置存储器,并且使INIT_B保持低电平,清空配置存储器的时间应该大于300us,之后INIT_B自动拉高,INIT_B拉高后才可以进行配置数据的加载。

能向你请教一下么,最近也在配selectMAP

你弄好了么,不知道还有什么可以帮忙的

你好,我想问一下SelectMAP模式共有D0-D7 8个接口,但是在画原理图时发现板子上只标明了D0(如图所示),那么D1-D7的接口到底在哪里?