UART发送程序的问题。

时间:10-02

整理:3721RD

点击:

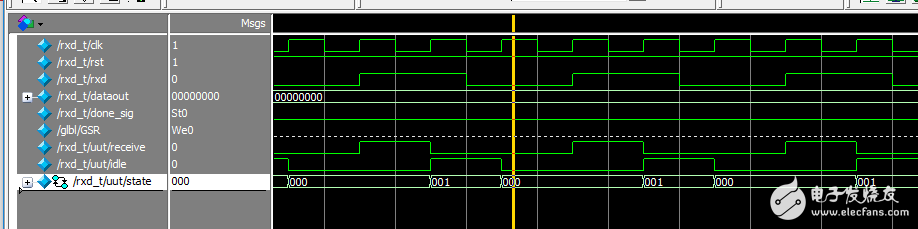

上代码,receive信号总是跳变,搞不清楚为什么会跳,然后cnt无法计数,无法进入接收数据的状态。脑袋都大了,到底哪里错了,进入不了state=001的接收程序中

module uart_rxd(clk,rst,rxd,dataout,done_sig

);

input clk,rst,rxd;

output dataout;

output done_sig;

reg [7:0] dataout;

reg done_sig;

reg [2:0] state;

reg [4:0] cnt;

reg odd_seg;

reg rxd_buff;

reg rxd_t;

reg idle;

reg receive;

always@(posedge clk)

begin

rxd_buff<=rxd;

rxd_t<=(rxd_buff&(~rxd));

end

always@(posedge clk or negedge rst)

begin

if(!rst)

begin receive<='b0; end

else if(rxd_t&&(~idle))

begin receive<='b1; end

else if(state<='b011) begin receive<='b0; end

end

always@(posedge clk or negedge rst)

begin

if(!rst)

begin

dataout<='b0;

state<='b0;

done_sig<='b0;

cnt<='b0;

idle<='b0;

end

else if(receive==1)

begin

case(state)

'b000:// 空闲

begin

state<='b001;

idle<='b1;

end

'b001: //开始接受数据

begin

idle<='b1;

case(cnt)

'd0:begin dataout[0]<=rxd;odd_seg<=(odd_seg&dataout[0]);cnt<=cnt+1;state<='b001; end

'd1:begin dataout[1]<=rxd;odd_seg<=(odd_seg&dataout[1]);cnt<=cnt+1;state<='b001; end

'd2:begin dataout[2]<=rxd;odd_seg<=(odd_seg&dataout[2]);cnt<=cnt+1; state<='b001;end

'd3:begin dataout[3]<=rxd;odd_seg<=(odd_seg&dataout[3]);cnt<=cnt+1; state<='b001;end

'd4:begin dataout[4]<=rxd;odd_seg<=(odd_seg&dataout[4]);cnt<=cnt+1;state<='b001; end

'd5:begin dataout[5]<=rxd;odd_seg<=(odd_seg&dataout[5]);cnt<=cnt+1; state<='b001;end

'd6:begin dataout[6]<=rxd;odd_seg<=(odd_seg&dataout[6]);cnt<=cnt+1;state<='b001; end

'd7:begin dataout[7]<=rxd;odd_seg<=(odd_seg&dataout[7]);cnt<=cnt+1;state<='b010; end

default: state<='b010;

endcase

end

'b010://奇偶校验

begin

idle<='b1;

if(rxd==odd_seg) begin state<='b011; end

else begin state<='b000; end

end

'b011://结束位

begin

idle<='b1;

if(rxd==1) begin done_sig<='b1; end

else begin done_sig<='b0;end

end

endcase

end

else

begin

idle<='b0;

done_sig<='b0;

state<='b000;

cnt<='b0;

end

end

endmodule