两种仿真软件仿真结果不一样怎么回事

时间:10-02

整理:3721RD

点击:

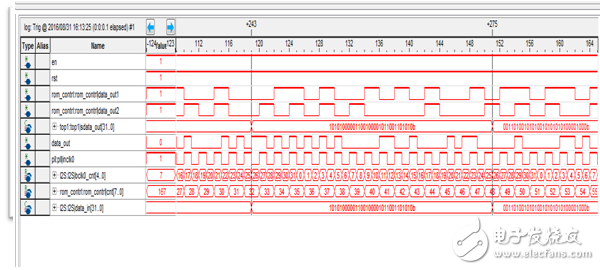

请问大家有谁遇到过modelsim与signaltap仿真结果不一样的情况,不知道什么原因引起的,请大家指教!

看不太清,但是给你说几点你注意一下

1. 输入模拟的是否和上板一样

2. 输入信号和内部处理是否是同一个时钟域

3. 时序约束是否通过

非常感谢您的回复,编译的时候发现时序报错。

你这个应该是没有做时序约束吧,都是unconstrained,不知道你时钟跑多少,如果100M一下时序问题应该不大,建议你还是看看跨时钟处理,,,