除頻器不會動作

时间:10-02

整理:3721RD

点击:

各位大大 小的最近在練習FPGA

目前有使用除頻器 及用modelsim來看其訊號 其code 如下1 2 所示

此除頻器有使用開發版子的七段顯示器來測試其功能 此除頻器可正常運作

但最近小弟用modelsim來看其訊號 卻沒有變動 不知是何原因 請各位大大指點> < 謝謝各位大大

1.除頻器

`timescale 1 ns / 100 ps

//除頻器

module divider(

output reg o_clk,

input rst_n,

input i_clk

);

parameter N=10_000_000;

parameter M=04_999_999;

reg [25:0]cnt;

always @(posedge i_clk or negedge rst_n)

begin

if(!rst_n)

cnt<=26'b0;

else

begin

if(cnt==N-1)

cnt<=26'b0;

else

cnt<=cnt+26'b1;

end

end

always @(posedge i_clk or negedge rst_n)

begin

if(!rst_n)

o_clk<=0;

else

begin

if(cnt<=M)

o_clk<=1;

else

o_clk<=0;

end

end

endmodule

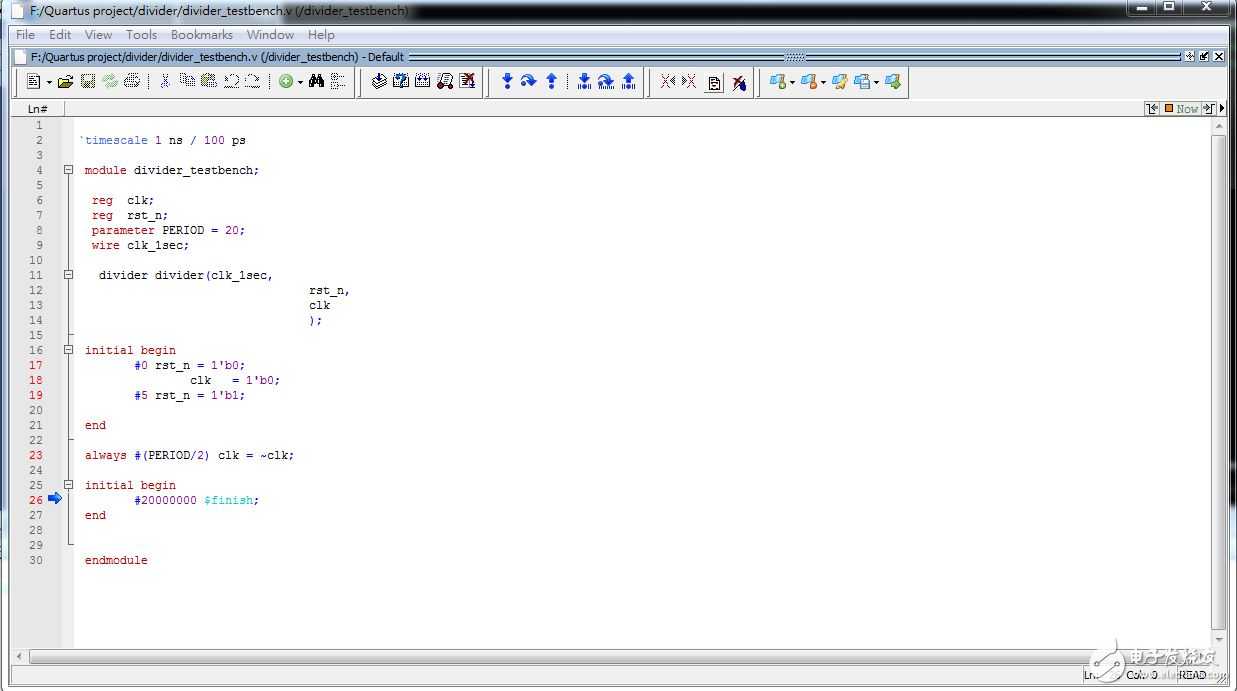

2.testbench

`timescale 1 ns / 100 ps

module divider_testbench;

reg clk;

reg rst_n;

parameter PERIOD = 20;

wire clk_1sec;

divider divider(clk_1sec,

rst_n,

clk

);

initial begin

#0 rst_n = 1'b0;

clk = 1'b0;

#5 rst_n = 1'b1;

end

always #(PERIOD/2) clk = ~clk;

initial begin

#20000000 $finish;

end

endmodule

圖1

目前有使用除頻器 及用modelsim來看其訊號 其code 如下1 2 所示

此除頻器有使用開發版子的七段顯示器來測試其功能 此除頻器可正常運作

但最近小弟用modelsim來看其訊號 卻沒有變動 不知是何原因 請各位大大指點> < 謝謝各位大大

1.除頻器

`timescale 1 ns / 100 ps

//除頻器

module divider(

output reg o_clk,

input rst_n,

input i_clk

);

parameter N=10_000_000;

parameter M=04_999_999;

reg [25:0]cnt;

always @(posedge i_clk or negedge rst_n)

begin

if(!rst_n)

cnt<=26'b0;

else

begin

if(cnt==N-1)

cnt<=26'b0;

else

cnt<=cnt+26'b1;

end

end

always @(posedge i_clk or negedge rst_n)

begin

if(!rst_n)

o_clk<=0;

else

begin

if(cnt<=M)

o_clk<=1;

else

o_clk<=0;

end

end

endmodule

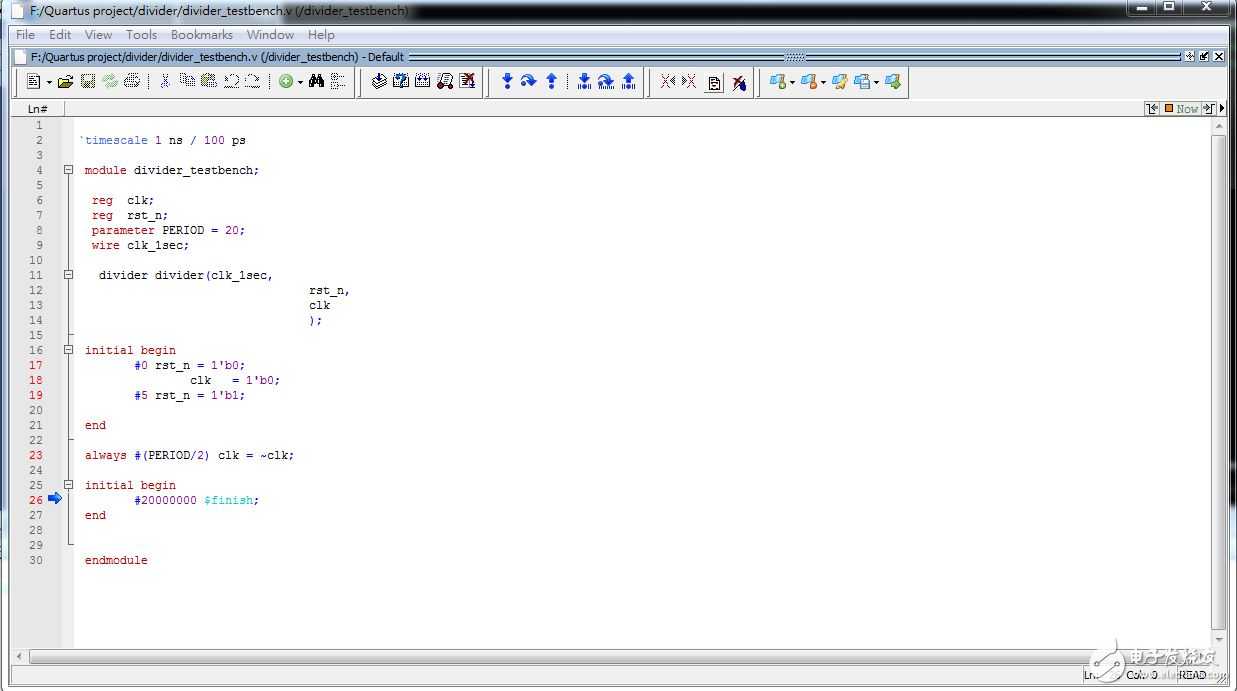

2.testbench

`timescale 1 ns / 100 ps

module divider_testbench;

reg clk;

reg rst_n;

parameter PERIOD = 20;

wire clk_1sec;

divider divider(clk_1sec,

rst_n,

clk

);

initial begin

#0 rst_n = 1'b0;

clk = 1'b0;

#5 rst_n = 1'b1;

end

always #(PERIOD/2) clk = ~clk;

initial begin

#20000000 $finish;

end

endmodule

圖1