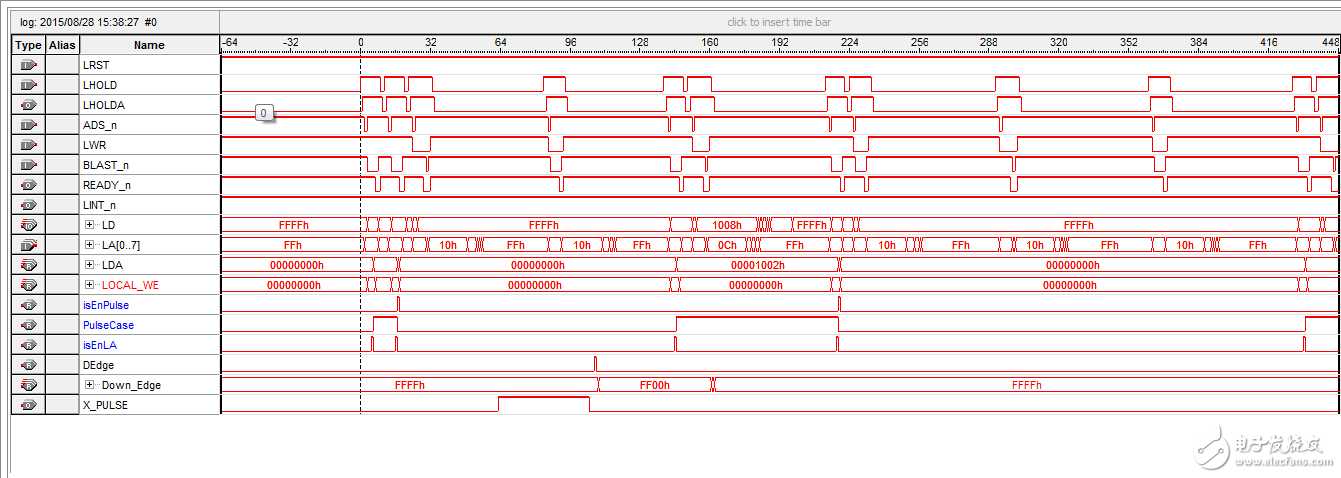

PCI9054与fpga通信时,读命令有延时,为什么,是驱动的问题吗,还是fpga程序的问题,请看下图

时间:10-02

整理:3721RD

点击:

如图所示:先发的是写命令(2个)+读命令(1个)+读命令(1个)+写命令(1个),可以看出写命令后可以紧跟着发送命令,而读命令,却需要时间才发送下一个指令,是什么问题?用的C模式target

图1

写命令CPU直接扔给桥片再到9054最后到FPGA,可以连着给出来的,因为不需要返回数据,而读取则要在数据最终返回到CPU之前保持传输通道空闲,即堵塞下一个IO操作,Window驱动里有相关描述,可能是叫IRP之类的内容吧

谢谢,我看一下这个流程,我刚开始接触驱动。这个驱动是个老版本,以前是与PCI9052+fpga连接起来用的,老版本就不会出现 读操作 延时的情况, 是不是fpga程序的问题/?

读确实需要时间呢,我查到了,谢谢, 这个读的时间可以缩短吗?

如果FPGA接口逻辑对读操作的响应延迟已经缩短到2clk之内的话就没什么可改进的了,只能在9054接口配置上下功夫,比如提高接口频率、用同步模式等

谢谢,我修改下9054配置

大神 请问一下你还有该设计的FPGA程序吗?如果方便的话请发给我一份 155468078@qq.com 多谢啊