大神们来帮帮忙,新手啊求教啊!

时间:10-02

整理:3721RD

点击:

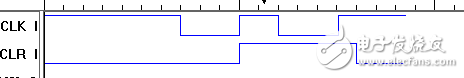

我想实现clk与clr同为上升沿时触发,让q=d,该怎么写呢?写出来只有clr在此时刻为高才可以,怎么办呢?

module dd8(Q, CLK, CLR, d);

output reg [7:0] Q;

input CLK, CLR;

input [7:0] d;

always @( )

begin

end

endmodule

希望在clk第一个上升沿来时,将输出q=d,如图file:///C:\Users\lenovo\AppData\Roaming\Tencent\Users\460815134\QQ\WinTemp\RichOle\8C7@7)C2@V6W}}J8(I6$AFM.png

always@(posedge clk & posedge clr)

或者你定义一个clk1<=clk & clr,然后always@(posedge clk1)

q<=d;

这是什么语言,看不懂啊!有点像C

Verilog啊,你不弄fpga啊

always @(posedge CLK )

if (RST)

begin

Q<=d;

end

endmodule

不行啊,clr没了呢,你的RST是clr吗

是,刚才写错了

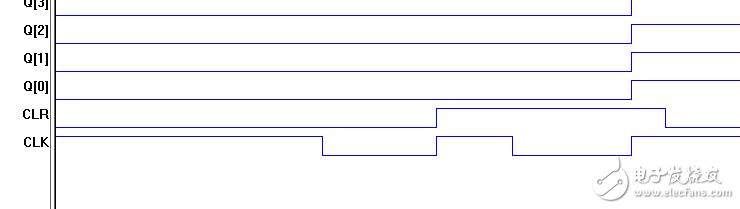

这个原来我也试过,只不过输出是这样的,不能检测到clr的上升沿

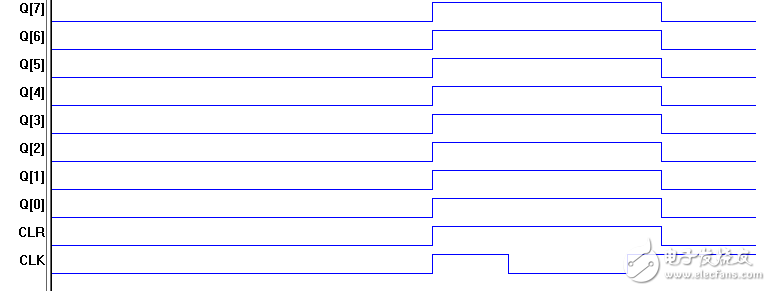

ok 用第二种方法还是可以的呢! 赞一个!

附加程序

module dd8(Q, CLK, CLR, d);

output reg [7:0] Q;

input CLK, CLR;

input [7:0] d;

wire CLK1;

assign CLK1=CLK&CLR;

always @( posedge CLK1 or negedge CLR )

begin

if (CLR)

Q<=d;

else

Q<=8'O0;

end

endmodule