关于SRAM/FRAM接口设计的问题求助

时间:10-02

整理:3721RD

点击:

目前使用的quartus版本为12.1

FPGA为cyclone5系列 5CEBA4U15C8N

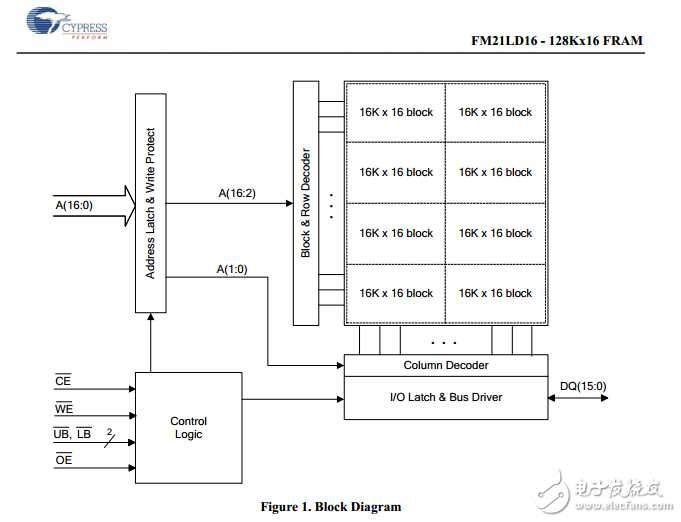

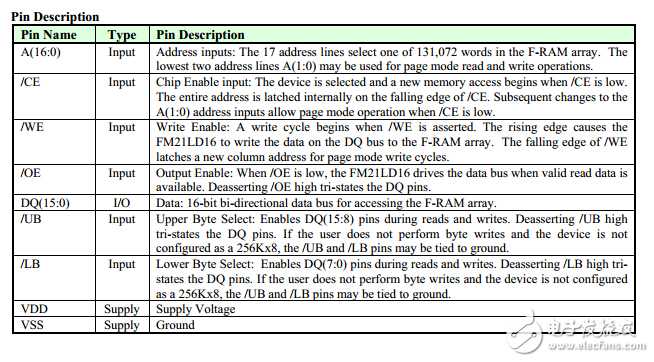

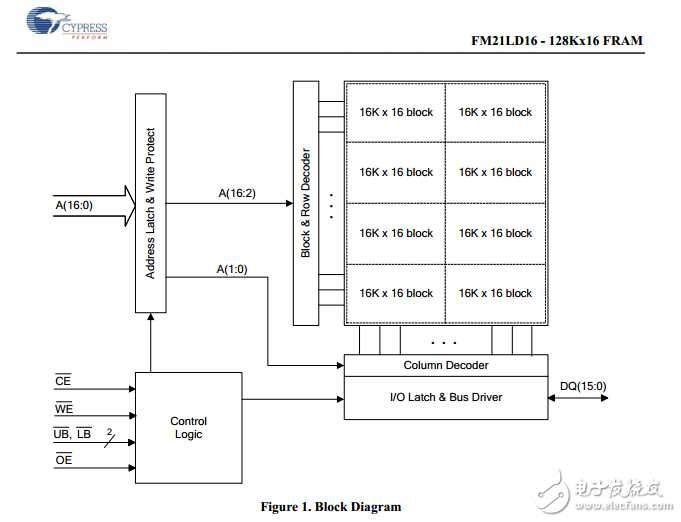

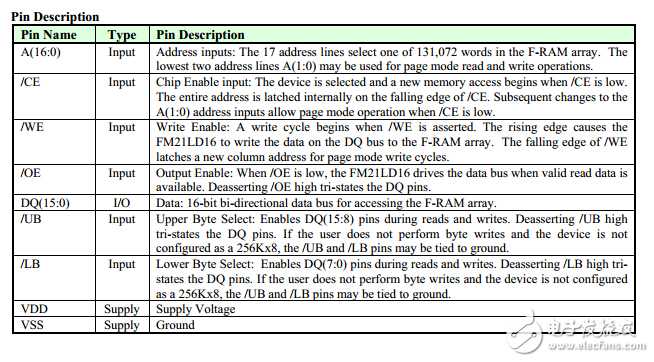

FRAM为 Cypress: FM21LD16-60(2Mbit)

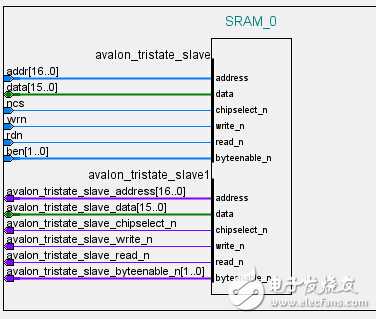

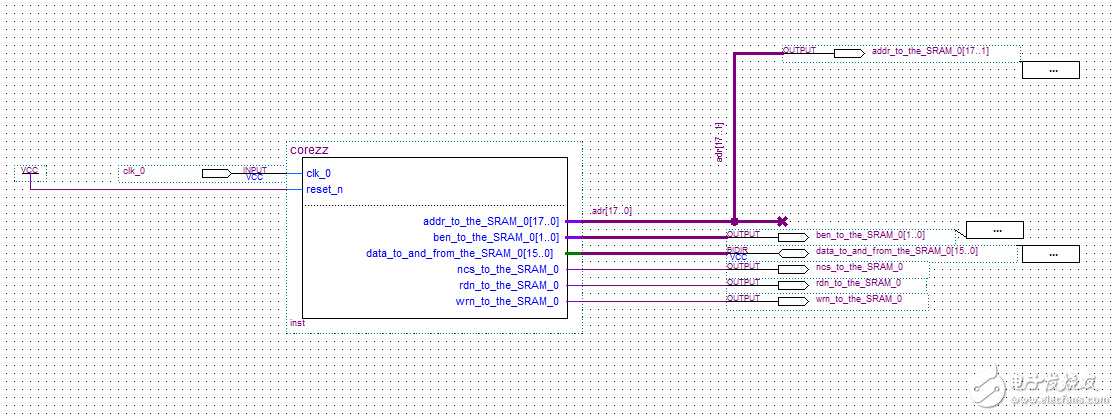

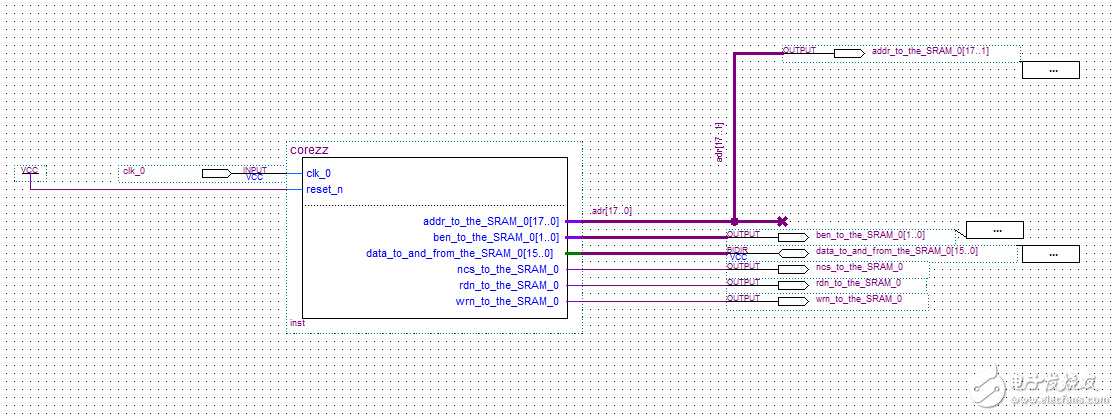

附上FRAM datasheet的部分和我设计的测试部分

烧进板子后用nios执行得到的就是“Verify failed between address xx and oo(fram地址部分)”的错误。对于FRAM的接口设计和使用不是很有把握,可能会有很多低级错误还望指教。

另附上FRAM的tcl代码

# TCL File Generated by Component Editor 12.1sp1

# Mon Dec 15 20:44:28 JST 2014

# DO NOT MODIFY

#

# SRAM "IS61WV51216" v1.0

# me 2014.12.15.20:44:28

# 16bit SRAM Interface

#

#

# request TCL package from ACDS 11.0

#

package require -exact sopc 11.0

#

# module SRAM

#

set_module_property DESCRIPTION "16bit SRAM Interface"

set_module_property NAME SRAM

set_module_property VERSION 1.0

set_module_property INTERNAL false

set_module_property OPAQUE_ADDRESS_MAP true

set_module_property GROUP SRAM

set_module_property AUTHOR me

set_module_property ICON_PATH output_files/

set_module_property DISPLAY_NAME IS61WV51216

set_module_property TOP_LEVEL_HDL_FILE output_files/

set_module_property INSTANTIATE_IN_SYSTEM_MODULE false

set_module_property EDITABLE true

set_module_property ANALYZE_HDL AUTO

set_module_property FIX_110_VIP_PATH false

set_module_property REPORT_TO_TALKBACK false

set_module_property ALLOW_GREYBOX_GENERATION false

#

# files

#

#

# file sets

#

#

# parameters

#

#

# display items

#

#

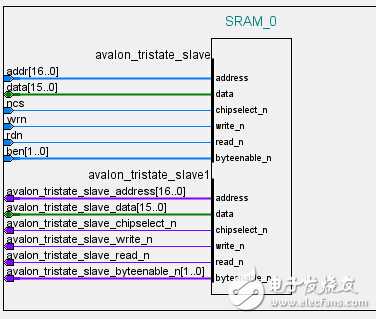

# connection point avalon_tristate_slave

#

add_interface avalon_tristate_slave avalon_tristate end

set_interface_property avalon_tristate_slave activeCSThroughReadLatency false

set_interface_property avalon_tristate_slave associatedClock ""

set_interface_property avalon_tristate_slave explicitAddressSpan 262144

set_interface_property avalon_tristate_slave holdTime 1

set_interface_property avalon_tristate_slave isMemoryDevice true

set_interface_property avalon_tristate_slave isNonVolatileStorage false

set_interface_property avalon_tristate_slave maximumPendingReadTransactions 0

set_interface_property avalon_tristate_slave printableDevice false

set_interface_property avalon_tristate_slave readLatency 0

set_interface_property avalon_tristate_slave readWaitTime 1

set_interface_property avalon_tristate_slave setupTime 0

set_interface_property avalon_tristate_slave timingUnits Cycles

set_interface_property avalon_tristate_slave writeWaitStates 1

set_interface_property avalon_tristate_slave writeWaitTime 1

set_interface_property avalon_tristate_slave ENABLED true

add_interface_port avalon_tristate_slave addr address Input 17

add_interface_port avalon_tristate_slave data data Bidir 16

add_interface_port avalon_tristate_slave ncs chipselect_n Input 1

add_interface_port avalon_tristate_slave wrn write_n Input 1

add_interface_port avalon_tristate_slave rdn read_n Input 1

add_interface_port avalon_tristate_slave ben byteenable_n Input 2

set_interface_assignment avalon_tristate_slave embeddedsw.configuration.isFlash 0

set_interface_assignment avalon_tristate_slave embeddedsw.configuration.isMemoryDevice 1

set_interface_assignment avalon_tristate_slave embeddedsw.configuration.isNonVolatileStorage 0

set_interface_assignment avalon_tristate_slave embeddedsw.configuration.isPrintableDevice 0

FPGA为cyclone5系列 5CEBA4U15C8N

FRAM为 Cypress: FM21LD16-60(2Mbit)

附上FRAM datasheet的部分和我设计的测试部分

烧进板子后用nios执行得到的就是“Verify failed between address xx and oo(fram地址部分)”的错误。对于FRAM的接口设计和使用不是很有把握,可能会有很多低级错误还望指教。

另附上FRAM的tcl代码

# TCL File Generated by Component Editor 12.1sp1

# Mon Dec 15 20:44:28 JST 2014

# DO NOT MODIFY

#

# SRAM "IS61WV51216" v1.0

# me 2014.12.15.20:44:28

# 16bit SRAM Interface

#

#

# request TCL package from ACDS 11.0

#

package require -exact sopc 11.0

#

# module SRAM

#

set_module_property DESCRIPTION "16bit SRAM Interface"

set_module_property NAME SRAM

set_module_property VERSION 1.0

set_module_property INTERNAL false

set_module_property OPAQUE_ADDRESS_MAP true

set_module_property GROUP SRAM

set_module_property AUTHOR me

set_module_property ICON_PATH output_files/

set_module_property DISPLAY_NAME IS61WV51216

set_module_property TOP_LEVEL_HDL_FILE output_files/

set_module_property INSTANTIATE_IN_SYSTEM_MODULE false

set_module_property EDITABLE true

set_module_property ANALYZE_HDL AUTO

set_module_property FIX_110_VIP_PATH false

set_module_property REPORT_TO_TALKBACK false

set_module_property ALLOW_GREYBOX_GENERATION false

#

# files

#

#

# file sets

#

#

# parameters

#

#

# display items

#

#

# connection point avalon_tristate_slave

#

add_interface avalon_tristate_slave avalon_tristate end

set_interface_property avalon_tristate_slave activeCSThroughReadLatency false

set_interface_property avalon_tristate_slave associatedClock ""

set_interface_property avalon_tristate_slave explicitAddressSpan 262144

set_interface_property avalon_tristate_slave holdTime 1

set_interface_property avalon_tristate_slave isMemoryDevice true

set_interface_property avalon_tristate_slave isNonVolatileStorage false

set_interface_property avalon_tristate_slave maximumPendingReadTransactions 0

set_interface_property avalon_tristate_slave printableDevice false

set_interface_property avalon_tristate_slave readLatency 0

set_interface_property avalon_tristate_slave readWaitTime 1

set_interface_property avalon_tristate_slave setupTime 0

set_interface_property avalon_tristate_slave timingUnits Cycles

set_interface_property avalon_tristate_slave writeWaitStates 1

set_interface_property avalon_tristate_slave writeWaitTime 1

set_interface_property avalon_tristate_slave ENABLED true

add_interface_port avalon_tristate_slave addr address Input 17

add_interface_port avalon_tristate_slave data data Bidir 16

add_interface_port avalon_tristate_slave ncs chipselect_n Input 1

add_interface_port avalon_tristate_slave wrn write_n Input 1

add_interface_port avalon_tristate_slave rdn read_n Input 1

add_interface_port avalon_tristate_slave ben byteenable_n Input 2

set_interface_assignment avalon_tristate_slave embeddedsw.configuration.isFlash 0

set_interface_assignment avalon_tristate_slave embeddedsw.configuration.isMemoryDevice 1

set_interface_assignment avalon_tristate_slave embeddedsw.configuration.isNonVolatileStorage 0

set_interface_assignment avalon_tristate_slave embeddedsw.configuration.isPrintableDevice 0

1.如果有时钟PLL 注意附加相移问题-65 到-75

2.FPGA的复位按键一定要接的是全局时钟引脚才可以

3.确定连线正确 你板子上的和你程序里的是否一致?