porcess外的信号赋值出错

时间:10-02

整理:3721RD

点击:

我写了一个实现转置的程序,程序里用到了双口RAM。写的程序主要是,将A口设置为写,B口设置为读。这些都没什么问题。 程序中用到了三个process,其中一个process如下,这个程序将dat_vld_o_buf信号赋值给dat_vld_o。没有语法错误。但是仿真时出错。单步仿真时的错误也截图了。到底哪里出了问题。

-----------结构体---------------------

process(clk_i,rst)

begin

IF(rst='0')THEN

dat_vld_o_buf<='0';

ELSIF(RISING_EDGE(CLK_I)) then

if(cnt="10001")then

dat_vld_o_buf<='1';

end if;

END IF;

end process;

addra_ram<=addra;-----这个可以赋值

addrb_ram<=addrb;--这个可以赋值

dat_vld_o <= dat_vld_o_buf;--这个完蛋了可以看modelsim中dat_vld_o一直为U.

-------------------------------------------

-----------结构体---------------------

process(clk_i,rst)

begin

IF(rst='0')THEN

dat_vld_o_buf<='0';

ELSIF(RISING_EDGE(CLK_I)) then

if(cnt="10001")then

dat_vld_o_buf<='1';

end if;

END IF;

end process;

addra_ram<=addra;-----这个可以赋值

addrb_ram<=addrb;--这个可以赋值

dat_vld_o <= dat_vld_o_buf;--这个完蛋了可以看modelsim中dat_vld_o一直为U.

-------------------------------------------

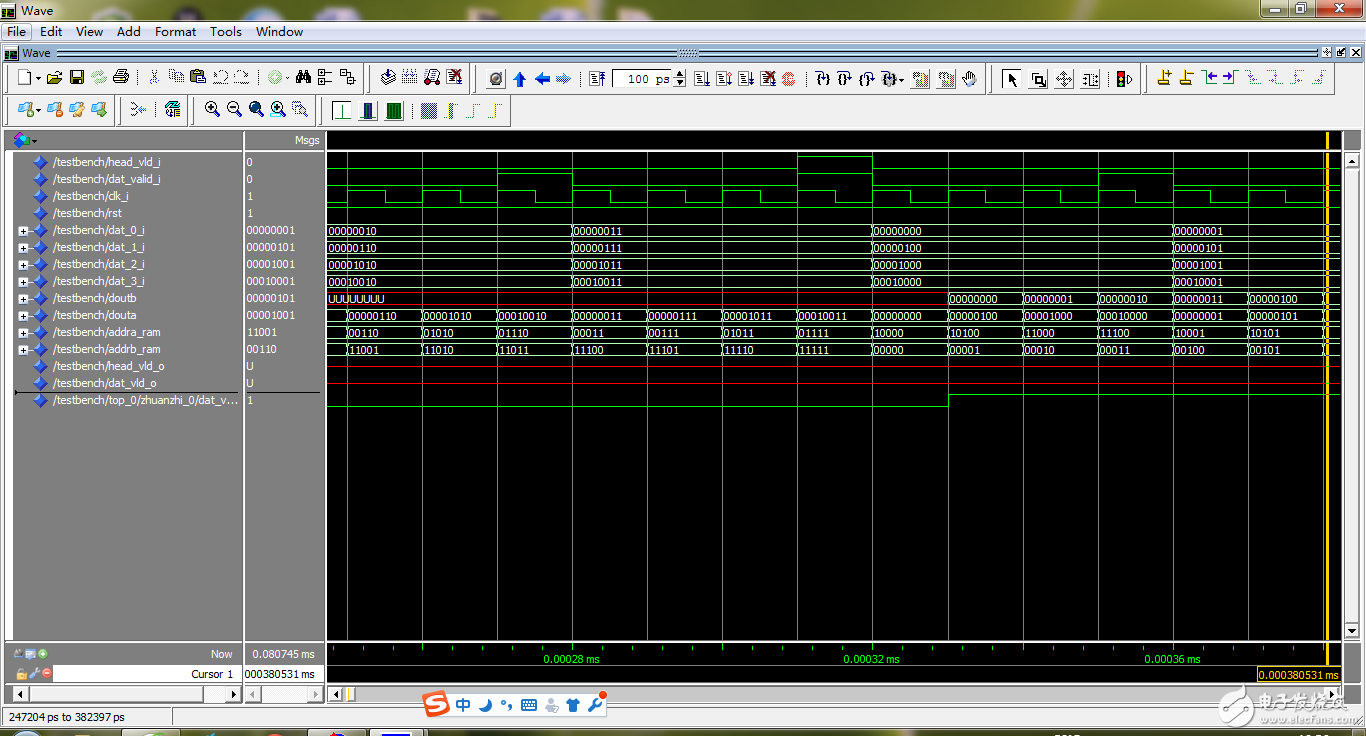

从仿真可以看出信号buf并没有赋值给dat_vld_o

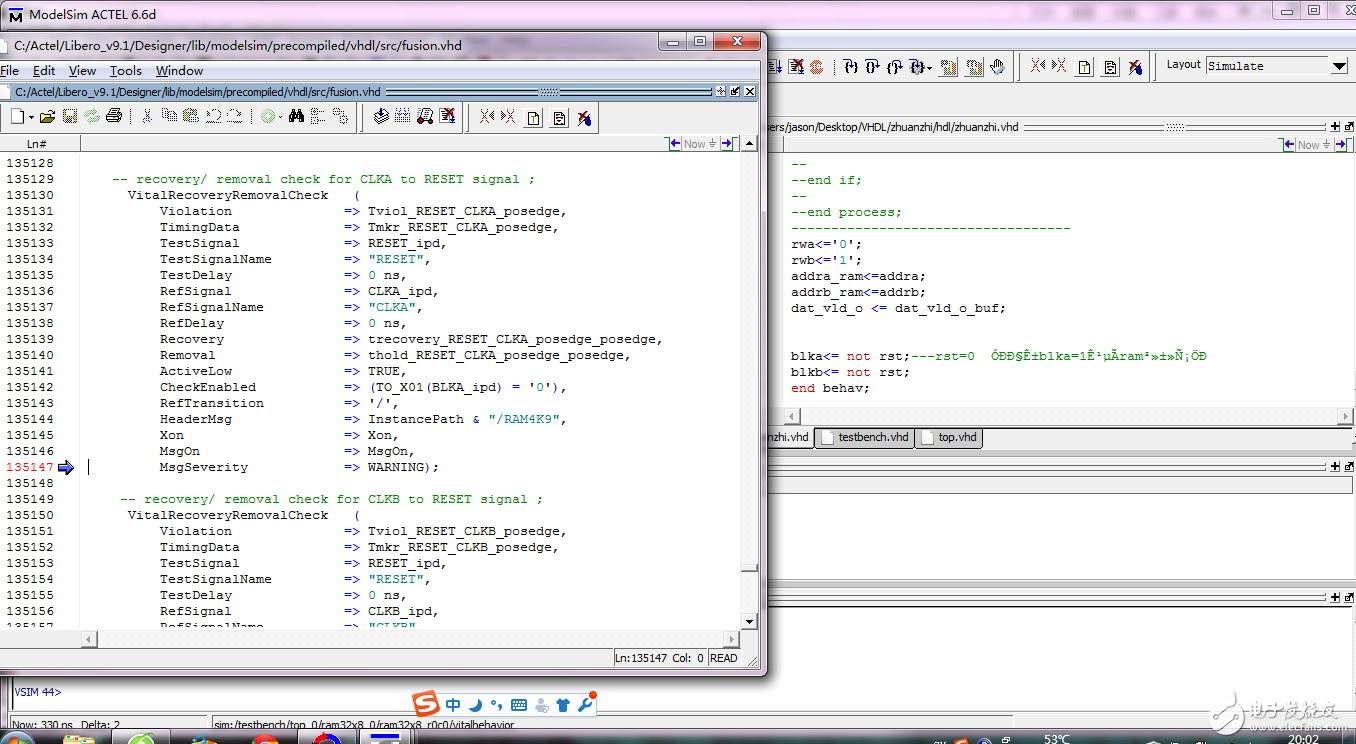

这个是我单步仿真到,dat_vld_o <= dat_vld_o_buf这个语句时显示出的调用fushion(actel fpga)窗口,似乎 ...

确认一下dat_vld_o是否被使用,有可能被优化了

这个仿真是我没有进行综合之前的仿真,应该不会被优化才对。

终于发现了原因,我再modelsim中仿真时的警告如下Uninitialized out port has no driver ,我仔细查看了发现我的testbench 文件中在例化模块时没有将port map()写完整。特此结贴。