Xilinx FPGA入门连载10:Modelsim仿真验证

特权同学,版权所有

配套例程和更多资料下载链接:

http://pan.baidu.com/s/1jGjAhEm

1 ISE基本设置

好,既然我们的语法检查通过了,那么接下来我们不妨小试牛刀,让仿真工具Modelsim来输出波形验证设计结果和我们的预想是否一致。

在用Modelsim仿真前,在ISE中需要确认几个设置。

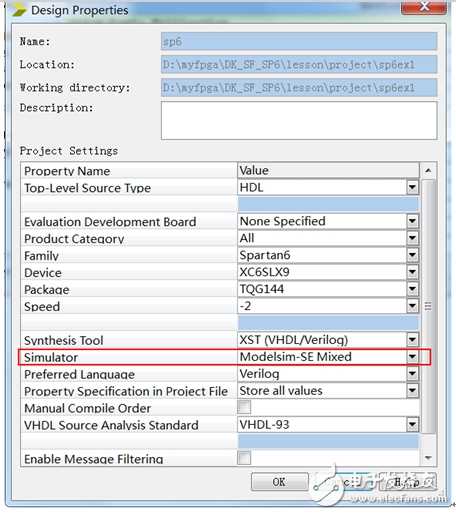

1. 如图所示,点击菜单的“Projectà Design Properties…”。

如图所示,确认这里“Simulator”的选择为“Modelsim-SEMixed”,这在新建工程时我们已经设定好了,为保万无一失,我们还是确认一下。

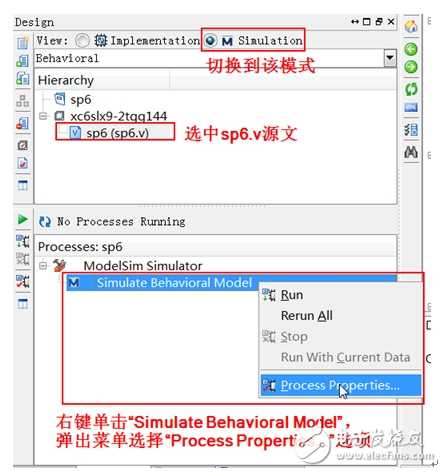

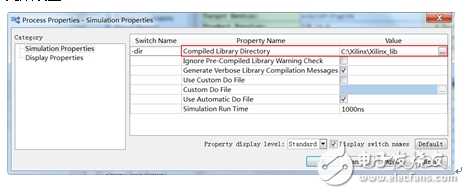

2. 如下图所示,从上到下依次执行3步操作。

弹出“Process Properties”设置窗口,在右边的“Compiled Library Directory”后面填入之前编译库时设置的已编译库的路径,点旁边的“…”按钮来选定也行。我们前面lesson中将库路径设置为“C:\Xilinx\Xilinx_lib”,因此这里也这么设置。其他选项默认设置即可,点击“OK” 完成设置。

2 测试脚本创建与编辑

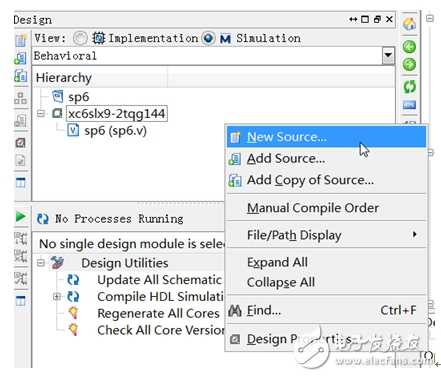

回到“Simulation à Hierarchy”窗口中,在任意空白处单击右键,弹出菜单中选择“New Source”,如图所示。

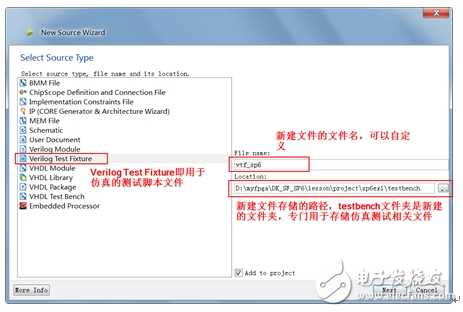

如图所示,选择新建源文件类型是“Verilog Test Fixture”,在工程路径下新建一个名为“testbench”的文件夹,同时将新建文件的路径定位到这个文件夹下面。和前面的lesson新建source_code文件夹的初衷一样,新建testbench文件夹的目的也只是为了便于文件的分类和管理。还有“Add to project”通常必须勾选上,默认即勾选。点击“Next”到下一步。

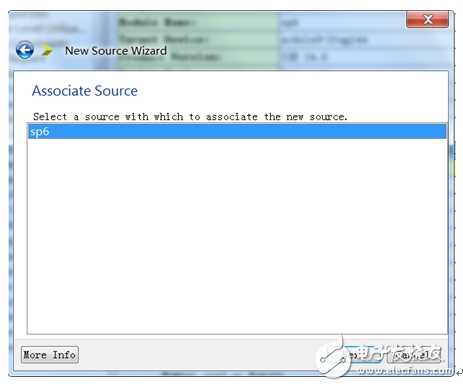

这里“Associate Source”是选择测试脚本对应的设计源文件,我们只有一个设计源文件,那就别无选择了,选中sp6.v,然后点击“Next”。

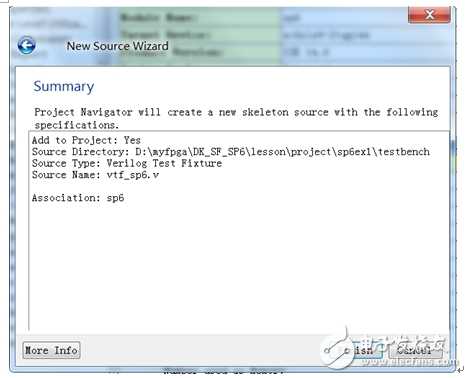

如图所示,罗列出前面设置的报告,没问题就点击“Finish”完成文件创建。

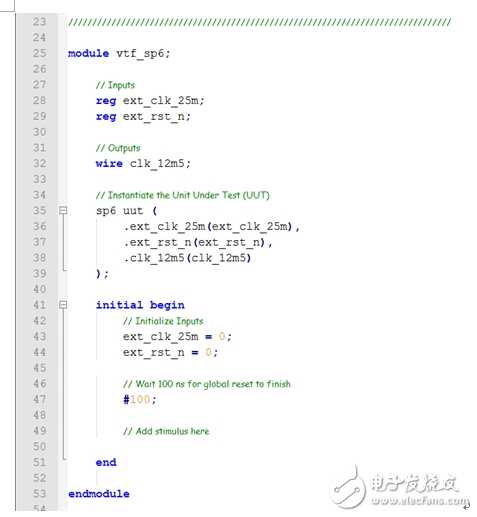

如图所示,测试脚本文件在Notepad++中打开了。这里的测试脚本只是一个基本的模板,它把设计文件sp6的接口在这个模块里面例化申明了,我们还需要自动动手添加复位和时钟的激励。

有朋友可能是第一次接触测试仿真,关于仿真的基本概念请查看《FPGA设计实战演练(逻辑篇)- ch9 - 设计仿真.pdf》。

Vtf_sp6.v文件需要做一些编辑,增加复位和时钟信号,修改后代码如下。

module vtf_sp6;

// Inputs

reg ext_clk_25m;

reg ext_rst_n;

// Outputs

wire clk_12m5;

// Instantiate the Unit Under Test(UUT)

sp6 uut (

.ext_clk_25m(ext_clk_25m),

.ext_rst_n(ext_rst_n),

.clk_12m5(clk_12m5)

);

initial begin

// Initialize Inputs

ext_clk_25m = 0;

ext_rst_n = 0;

// Wait 100 ns for globalreset to finish

#100;

ext_rst_n = 1;

// Add stimulus here

#2000;

$stop;

end

always #20 ext_clk_25m = ~ ext_clk_25m; //产生25MHz时钟源

endmodule

3 调用Modelsim仿真

保存修改后的代码。我们回到ISE中。

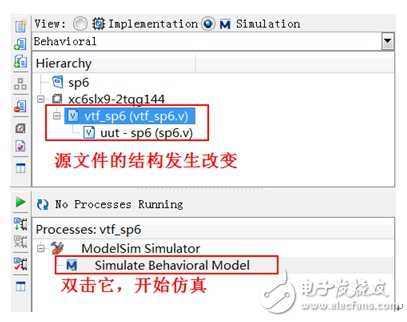

此时,如下图所示,vtf_sp6.v已经成了这个仿真Hierarchy的顶层了,它下面是设计文件sp6.v。我们选中vtf_sp6.v文件,然后双击“Simulation Behavioral Model”,随后Modelsim将被调用,启动仿真。

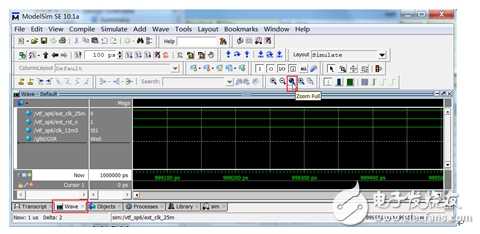

弹出Modelsim后,我们可以打开Wave查看,同时点击“Zoom Full”按钮,Modelsim的使用并不难,大家要多动手,所有的菜单按钮都简单易懂,有些地方右键菜单也有很多功能,如果这里一一介绍恐怕需要一本书,所以大家自动动手,贵在尝试,很快就会上手。

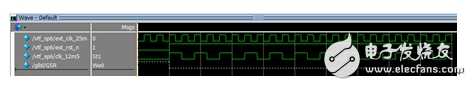

如图所示,这便是我们设计的二分频效果。

怎么样,通过这个简单的工程,大家是不是掌握了使用ISE进行工程创建、设计文本创建和编辑、测试脚本创建和编辑、使用Modelsim进行仿真等基本的技能。当然了,这只是刚刚把您领进门,让您熟悉一下工具的一些基本操作。这个例程就到这里,我们不往下进行板级的实验,大家继续跟着教程往下,该掌握的都会掌握滴。