altera FIFO IP核数据写入不进去

时间:10-02

整理:3721RD

点击:

电路如下图clk=50Mhz

wrclk经divide分频为10kzh

LIBRARY IEEE;

USE IEEE.std_logic_1164.ALL;

USE IEEE.std_logic_unsigned.ALL;

ENTITY devide is

port(clk:in std_logic;

reset:in std_logic;

clock:out std_logic

);

end devide;

architecture arch_devide of devide is

signal counter:integer range 0 to 99999999;

signal tmp_clk:std_logic;

begin

process

begin

wait until rising_edge(clk);

if(reset='0')then

counter<=0;

tmp_clk<='1';

else

if(counter=2499)then

counter<=0;

tmp_clk<=not tmp_clk;

else

counter<=counter+1;

end if;

end if;

end process;

clock<=tmp_clk;

end arch_devide;

wrreq设定为:复位后拉高十秒后拉低

LIBRARY IEEE;

USE IEEE.std_logic_1164.ALL;

USE IEEE.std_logic_unsigned.ALL;

ENTITY wrreq is

port(clk:in std_logic;

reset:in std_logic;

wrreq:out std_logic

);

end wrreq;

architecture arch_wrreq of wrreq is

signal counter:integer range 0 to 999999999;

signal tmp:std_logic;

begin

process

begin

wait until rising_edge(clk);

if(reset='0')then

counter<=0;

tmp<='1';

else

if(counter=499999999)then

tmp<='0';

else

counter<=counter+1;

end if;

end if;

end process;

wrreq<=tmp;

end arch_wrreq;

为什么一直为空写不进数据呢?

wrclk经divide分频为10kzh

LIBRARY IEEE;

USE IEEE.std_logic_1164.ALL;

USE IEEE.std_logic_unsigned.ALL;

ENTITY devide is

port(clk:in std_logic;

reset:in std_logic;

clock:out std_logic

);

end devide;

architecture arch_devide of devide is

signal counter:integer range 0 to 99999999;

signal tmp_clk:std_logic;

begin

process

begin

wait until rising_edge(clk);

if(reset='0')then

counter<=0;

tmp_clk<='1';

else

if(counter=2499)then

counter<=0;

tmp_clk<=not tmp_clk;

else

counter<=counter+1;

end if;

end if;

end process;

clock<=tmp_clk;

end arch_devide;

wrreq设定为:复位后拉高十秒后拉低

LIBRARY IEEE;

USE IEEE.std_logic_1164.ALL;

USE IEEE.std_logic_unsigned.ALL;

ENTITY wrreq is

port(clk:in std_logic;

reset:in std_logic;

wrreq:out std_logic

);

end wrreq;

architecture arch_wrreq of wrreq is

signal counter:integer range 0 to 999999999;

signal tmp:std_logic;

begin

process

begin

wait until rising_edge(clk);

if(reset='0')then

counter<=0;

tmp<='1';

else

if(counter=499999999)then

tmp<='0';

else

counter<=counter+1;

end if;

end if;

end process;

wrreq<=tmp;

end arch_wrreq;

为什么一直为空写不进数据呢?

太难了,没理解上去。

难么?就一个FIFO呀,我也是初学者,检查了一下wrclk和wrreq都没什么问题,就是empty标志位一直显示空

顶,求关注

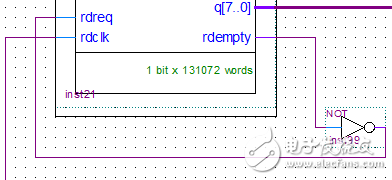

经检查成功写入,但是rdempty始终为1,

大概是rdempty到rdreq反馈的问题:

如果用反馈,就有上述现象出现;

如果不用反馈单独设置rdreq,则可以正常读写

那么问题就变成了这样的反馈为什么会出现问题,反馈如下图

我个人觉得可能是非门存在时延造成时序不匹配。