麻烦讲解一下这段FPGA程序

时间:10-02

整理:3721RD

点击:

首先叙述一下 这个程序是一个PCM编码程序的一部分 [qq]861831106[/qq]

但是因为是初学 程序的很多地方看不懂 不知道每个子程序的作用

程序的注释 我用中文表明了

我想请问一下 有没有会的大神 能够讲解一下 每一个子程序的作用是什么 谢谢! 谢谢帮助!

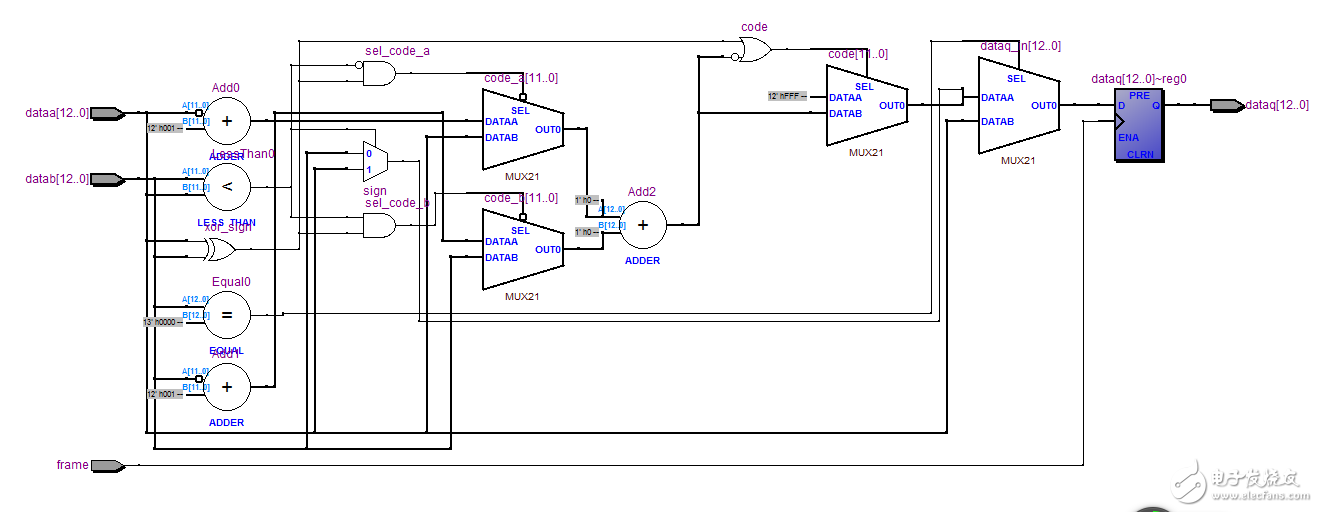

下面是主程序的RTL图 和 最后那个程序的电路图

主程序————————————————————————————————————————————————————————————library ieee;

use ieee.std_logic_1164.all;

entity alaw_l_nl is

port(

data :in std_logic_vector(12 downto 0); --pcm linear signal线性pcm信号

clock :in std_logic; --system clock系统时钟

frame :in std_logic; --frame synchronous signal帧同步信号

ebi :in std_logic; --enable even bit(a-law) inversion.1:inverted;0:not inverted

dataq :out std_logic); --output overlap signal输出信号重叠

end alaw_l_nl;

architecture structure of alaw_l_nl is

COMPONENT alaw_13_8

PORT(

data :in std_logic_vector(12 downto 0); --linear signal 线性信号

frame :in std_logic; --frame synchronous signal帧同步信号

dataq :out std_logic_vector(7 downto 0)); --output nolinear signal输出非线性信号

END COMPONENT;

COMPONENT alaw_invert

PORT(

data :in std_logic_vector(7 downto 0); --pcm nolinear signalpcm非线性信号

-- frame :in std_logic; --frame synchronous signal帧同步信号

ebi :in std_logic; --enable even bit(a-law) inversion.1:inverted;0:not inverted

dataq :out std_logic_vector(7 downto 0)); --output inversion signal反转信号输出

END COMPONENT;

COMPONENT p_s

PORT(

data :in std_logic_vector(7 downto 0); --pcm linear signal线性pcm信号

clock :in std_logic; --clock signal时钟信号

frame :in std_logic; --frame signal帧信号

dataq :out std_logic); --output overlap signal输出信号重叠

END COMPONENT;

signal data_p_s,data_invert :std_logic_vector(7 downto 0);

begin

u1:alaw_13_8

port map(data => data,

frame => frame,

dataq => data_invert);

u2:alaw_invert

port map(data => data_invert,

-- frame => frame,

ebi => ebi,

dataq => data_p_s);

u3:p_s

port map(data => data_p_s,

clock => clock,

frame => frame,

dataq => dataq);

end structure;

子程序1————————————————————————————————————————————————————————————

library ieee;

use ieee.std_logic_1164.all;

--use ieee.std_logic_unsigned.all;

entity alaw_13_8 is

PORT(

data :in std_logic_vector(12 downto 0); --pcm linear signal

frame :in std_logic; --frame synchronous signal

dataq :out std_logic_vector(7 downto 0)); --output noliear signal

end alaw_13_8;

architecture rtl of alaw_13_8 is

signal data_in :std_logic_vector(6 downto 0);

begin

process(data)

begin

if data(11) = '1' then

data_in integer_b else

'0';

sign <= dataa(12) when sel_sign = '1' else

datab(12);

xor_sign <= dataa(12) xor datab(12);

sel_code_a <= xor_sign and (not sel_sign);

sel_code_b <= xor_sign and sel_sign;

code_a <= dataa(11 downto 0) when sel_code_a = '0' else un_a;

code_b <= datab(11 downto 0) when sel_code_b = '0' else un_b;

code_tmp <= ('0' & code_a) + ('0' & code_b) ;

code <= code_tmp(11 downto 0) when code_tmp(12) = '0' or xor_sign = '1' else

"111111111111";

dataq_in <= dataa when datab = "0000000000000" else

-- dataq <= datab when dataa = "0000000000000" else

sign & code;

process(frame)

begin

if rising_edge(frame) then

dataq <= dataq_in;

end if;

end process;

end rtl;

————————————————————————————————————————————————————————————————

首先叙述一下 这个程序是一个PCM编码程序的一部分 [qq]861831106[/qq]

但是因为是初学 程序的很多地方看不懂 不知道每个子程序的作用

程序的注释 我用中文表明了

我想请问一下 有没有会的大神 能够讲解一下 每一个子程序的作用是什么 谢谢! 谢谢帮助!

下面是主程序的RTL图 和 最后那个程序的电路图

程序只是 多 其实不复杂 因为刚开始学习 希望好心人可以帮忙简单 说一下每部分的功能!

有没有人能教一下我。

没有人看到吗?

一个人都没有吗?

还没有人吗?

好失望

小编你这样大段的程序可能大家没有什么耐心看的哦!建议你把不懂的地方标明清楚。