请教一下DDS技术的频率分辨率的问题

时间:10-02

整理:3721RD

点击:

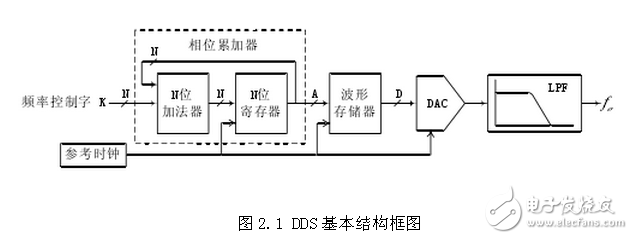

如图所示,典型的DDS主要由相位累加器,波形表,DA转换器和低通滤波器组成,其中相位累加器又包含一个全加器和一个相位寄存器。由相位寄存器输出地址对波形表进行索引,实现波形的输出,但在实际中,为了节省波形表的存储空间,只取地址的高M位作为波形表的地址值。那既然如此,为什么输出波形的分辨率会是参考时钟频率fc除以2N,而不是除以2M呢?

论坛里没有人用过DDS技术吗?坐等指导

什么意思?可以解释详细一点不?

分频啊,是对时钟频率进行分频,我主要不明白的还是为什么分辨率是这样计算的

此话怎讲?这跟波特率的计算方法有什么相似之处吗

频率控制字是m位,累加后取前n位做查找表地址

这个我明白,按照这个理论的话频率分辨率应该是fc除以2N没问题,但是在这后边有一个截断的问题,就是只用了地址的前M位,举个例子来说吧,如果N=10,M=8,fc=10K,那么当K=1,2,3,4时通过截断后的地址应该是同一个地址,那也就是说K每增加2(N-M)时,输出的是同一个地址的值,那就是说分辨率应该是fc除以2M才对啊,为什么是fc除以2N呢?还是说我的理解有错误呢?