建立时间和保持时间讨论

时间:10-02

整理:3721RD

点击:

建立时间(Setup Time):是指在触发器的时钟信号上升沿到来以前,数据稳定不变的时间,如果建立时间不够,数据将不能在这个时钟上升沿被输入触发器;

保持时间(HoldTime):是指在触发器的时钟信号上升沿到来以后,数据稳定不变的时间, 如果保持时间不够,数据同样不能被打入触发器。

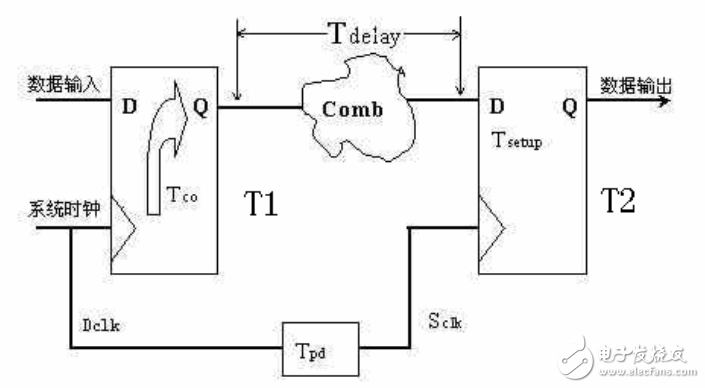

如图片中所示:

我们假设 T1,T2 寄存器是一条路径上的相连的两个寄存器,数据输入到 T1 经过1 个 clk 之后,传输到 T2;

Tco 为经过寄存器 T1 的传输延时;

Tdelay 为经过组合逻辑的传输延时;

Tsetup 为 T2 的建立时间;

Tpd 为时钟到 T1 和 T2 的偏差;

在一个时钟周期 T 之内,数据从寄存器 T1 传出,需要经过延时 Tco,然后经过组合逻辑,需要经过延时 Tdelay,最后到达寄存器 T2,然后在寄存器 T2 建立起来,需要经过延时 Tsetup,那么可以得出建立时间的要求:

Tsetup T2co(min);

各位朋友有什么见解请一起讨论

已经想通了,就应该是 Thold <= T1co(min) + Tdelay(min);

基本同步电路