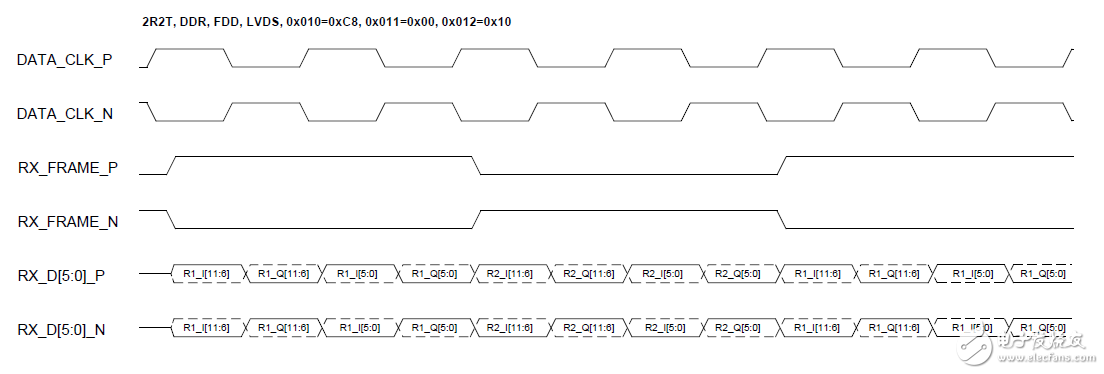

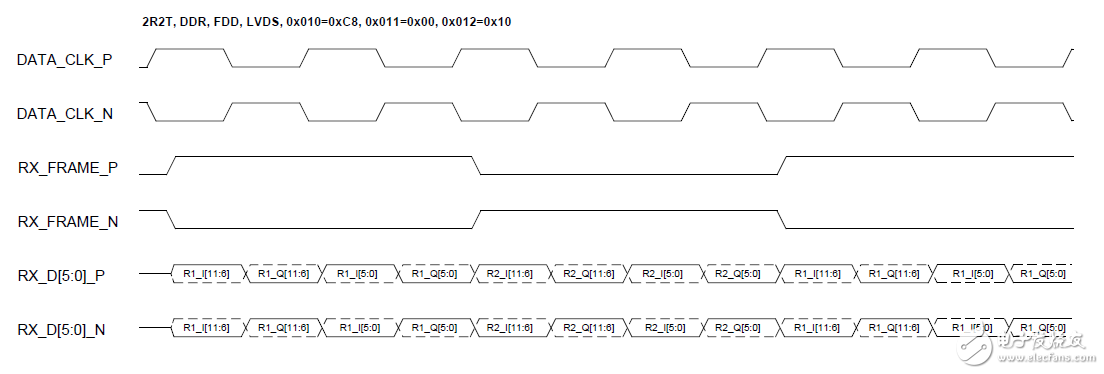

差分数据读取

时间:10-02

整理:3721RD

点击:

新手 求分析上面的时序 万分感谢!

有钱就好办事。

rx_frame的一个CLK周期是1组数据R1和R2的 12位输入、输出读写。以P为参考的话,上升沿对应R_Q,下降沿对应R_I.先转高位[11:6],再传低位。大概这思路,请参考。

有钱就好办事。

rx_frame的一个CLK周期是1组数据R1和R2的 12位输入、输出读写。以P为参考的话,上升沿对应R_Q,下降沿对应R_I.先转高位[11:6],再传低位。大概这思路,请参考。