使用quartusII fir ip核没有输出?

我把生成的fir.v进行了一点儿修改,如下(fenpin是我自己写的一个module,经测试输出的clk1和和clk2都没有问题):

module fir (

clk,

reset_n,

ast_sink_data,

ast_source_data,

ast_sink_ready,

ast_source_valid,

ast_source_error,

clk1,

clk2);

input clk;

input reset_n;

input [11:0] ast_sink_data;

reg ast_sink_valid=0;

reg ast_source_ready=0;

reg [1:0] ast_sink_error=00;

output [13:0] ast_source_data;

output ast_sink_ready;

output ast_source_valid;

output [1:0] ast_source_error;

output clk1,clk2;

fenpin #(625,1,1) fp(clk,clk1);

assign clk2=clk1;

initial

begin

#10 ast_sink_valid<=1;

ast_source_ready<=1;

end

fir_ast fir_ast_inst(

.clk(clk),

.reset_n(reset_n),

.ast_sink_data(ast_sink_data),

.ast_sink_valid(ast_sink_valid),

.ast_source_ready(ast_source_ready),

.ast_sink_error(ast_sink_error),

.ast_source_data(ast_source_data),

.ast_sink_ready(ast_sink_ready),

.ast_source_valid(ast_source_valid),

.ast_source_error(ast_source_error));

endmodule

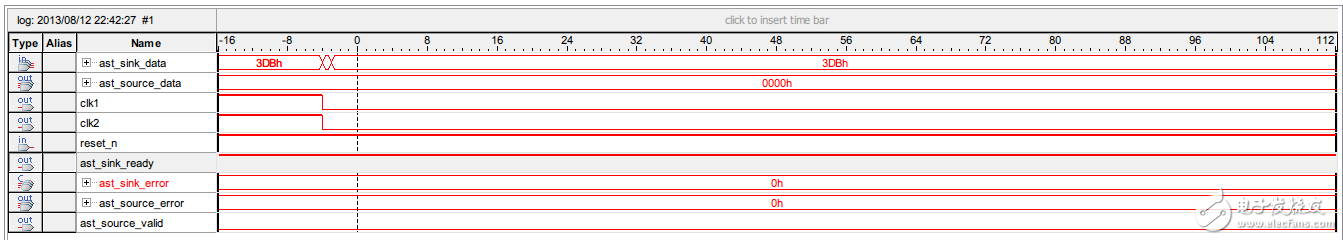

这是我们用signaltap抓取的,输出一直是0,ast_source_valid也一直是0,不知道是为什么啊?

我把生成的fir.v进行了一点儿修改,如下(fenpin是我自己写的一个module,经测试输出的clk1和和clk2都没有问题):

- module fir (

- clk,

- reset_n,

- ast_sink_data,

- ast_source_data,

- ast_sink_ready,

- ast_source_valid,

- ast_source_error,

- clk1,

- clk2);

- input clk;

- input reset_n;

- input [11:0] ast_sink_data;

- reg ast_sink_valid=0;

- reg ast_source_ready=0;

- reg [1:0] ast_sink_error=00;

- output [13:0] ast_source_data;

- output ast_sink_ready;

- output ast_source_valid;

- output [1:0] ast_source_error;

- output clk1,clk2;

-

- fenpin #(625,1,1) fp(clk,clk1);

- assign clk2=clk1;

-

- initial

- begin

- #10 ast_sink_valid<=1;

- ast_source_ready<=1;

- end

- fir_ast fir_ast_inst(

- .clk(clk),

- .reset_n(reset_n),

- .ast_sink_data(ast_sink_data),

- .ast_sink_valid(ast_sink_valid),

- .ast_source_ready(ast_source_ready),

- .ast_sink_error(ast_sink_error),

- .ast_source_data(ast_source_data),

- .ast_sink_ready(ast_sink_ready),

- .ast_source_valid(ast_source_valid),

- .ast_source_error(ast_source_error));

- endmodule

我有点疑问就是,你用initial放到综合代码中,编译器是否可以综合通过的问题。第29--32行.

可以通过编译的,就算没有initial这一点依然是没有任何输出的

同样的问题不知道怎么解决。同求

我用quartus的FIR的IP核仿真输出全是高阻,是怎么回事啊?

IP核。.。