三角波程序时序仿真产生毛刺啊?

时间:10-02

整理:3721RD

点击:

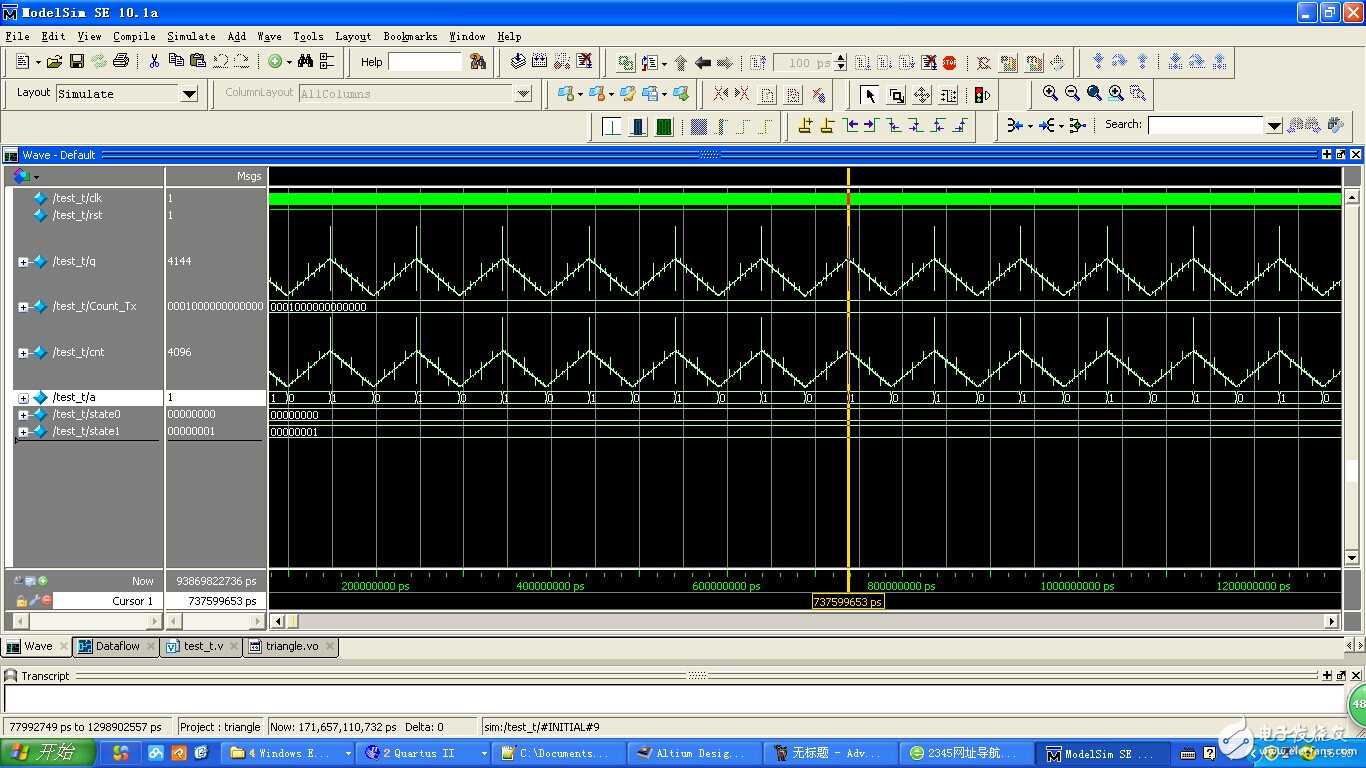

这个是我三角波的程序,但是用modelsim做时序仿真时产生这么多的毛刺,请问是怎么回事啊?

//clk = 81.92mhz

module triangle(clk,rst,q,Count_Tx,cnt,a,state0,state1);

input clk,rst;

// input [15:0] striangle_count;

output [15:0] q;

output [15:0] Count_Tx;

output [15:0] cnt;

output [7:0] a,state0,state1;

reg [15:0] cnt=0;

reg [7:0] a;

reg [15:0] Count_Tx=4096;

reg [15:0] q;

always @ (posedge clk)begin

if(!rst)begin

cnt = Count_Tx)begin

a <= 1;

cnt<=Count_Tx-1'b1;end

else

cnt <= cnt + 1'b1;

end

else if(a == 1)begin

if(cnt <= 16'b0000)begin

a <= 0;

cnt <=1'b1;end

else

cnt<=cnt-1'b1;

end

end

q <= cnt;

end

endmodule

程序逻辑有问题 建议认真 理清楚思路