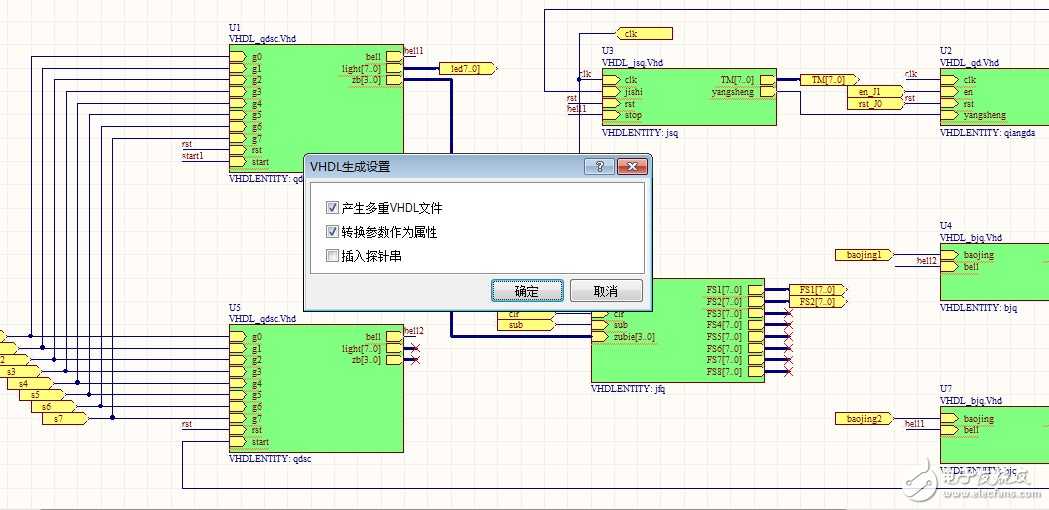

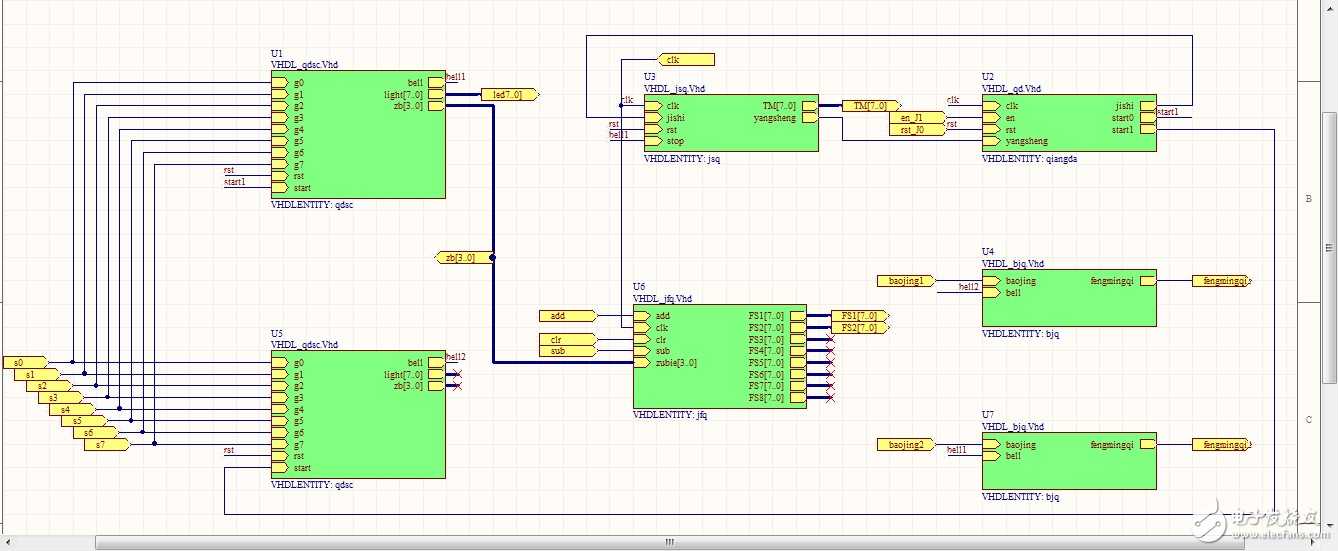

求助!用altium designer 6.9设计八路智能抢答器时遇到的困难

以下是生成的VHDL文件:

以下是生成的VHDL文件:------------------------------------------------------------

-- VHDL Sheet_xiugaiban

-- 2014 5 7 22 0 32

-- Created By "Altium Designer VHDL Generator"

-- "Copyright (c) 2002-2004 Altium Limited"

------------------------------------------------------------

------------------------------------------------------------

-- VHDL Sheet_xiugaiban

------------------------------------------------------------

Library IEEE;

Use IEEE.std_logic_1164.all;

Entity FPGA_Project_xiugaiban Is

port

(

ADD : In STD_LOGIC;

BAOJING1 : In STD_LOGIC;

BAOJING2 : In STD_LOGIC;

CLK : In STD_LOGIC;

CLR : In STD_LOGIC;

EN_J1 : In STD_LOGIC;

FENGMINGQI1 : Out STD_LOGIC;

FENGMINGQI2 : Out STD_LOGIC;

FS1 : Out STD_LOGIC_VECTOR(7 DOWNTO 0);

FS2 : Out STD_LOGIC_VECTOR(7 DOWNTO 0);

LED7_0 : Out STD_LOGIC;

RST_J0 : In STD_LOGIC;

S0 : In STD_LOGIC;

S1 : In STD_LOGIC;

S2 : In STD_LOGIC;

S3 : In STD_LOGIC;

S4 : In STD_LOGIC;

S5 : In STD_LOGIC;

S6 : In STD_LOGIC;

S7 : In STD_LOGIC;

SUB : In STD_LOGIC;

TM : Out STD_LOGIC_VECTOR(7 DOWNTO 0);

ZB : Out STD_LOGIC_VECTOR(3 DOWNTO 0)

);

attribute MacroCell : boolean;

End FPGA_Project_xiugaiban;

------------------------------------------------------------

------------------------------------------------------------

architecture structure of FPGA_Project_xiugaiban is

Component bjq

port

(

baojing : in STD_LOGIC;

bell : in STD_LOGIC;

fengmingqi : out STD_LOGIC

);

End Component;

Component jfq

port

(

add : in STD_LOGIC;

clk : in STD_LOGIC;

clr : in STD_LOGIC;

FS1 : out STD_LOGIC_VECTOR(7 downto 0);

FS2 : out STD_LOGIC_VECTOR(7 downto 0);

FS3 : out STD_LOGIC_VECTOR(7 downto 0);

FS4 : out STD_LOGIC_VECTOR(7 downto 0);

FS5 : out STD_LOGIC_VECTOR(7 downto 0);

FS6 : out STD_LOGIC_VECTOR(7 downto 0);

FS7 : out STD_LOGIC_VECTOR(7 downto 0);

FS8 : out STD_LOGIC_VECTOR(7 downto 0);

sub : in STD_LOGIC;

zubie : in STD_LOGIC_VECTOR(3 downto 0)

);

End Component;

Component jsq

port

(

clk : in STD_LOGIC;

jishi : in STD_LOGIC;

rst : in STD_LOGIC;

stop : in STD_LOGIC;

TM : out STD_LOGIC_VECTOR(7 downto 0);

yangsheng : out STD_LOGIC

);

End Component;

Component qdsc

port

(

bell : out STD_LOGIC;

g0 : in STD_LOGIC;

g1 : in STD_LOGIC;

g2 : in STD_LOGIC;

g3 : in STD_LOGIC;

g4 : in STD_LOGIC;

g5 : in STD_LOGIC;

g6 : in STD_LOGIC;

g7 : in STD_LOGIC;

light : out STD_LOGIC_VECTOR(7 downto 0);

rst : in STD_LOGIC;

start : in STD_LOGIC;

zb : out STD_LOGIC_VECTOR(3 downto 0)

);

End Component;

Component qiangda

port

(

clk : in STD_LOGIC;

en : in STD_LOGIC;

jishi : out STD_LOGIC;

rst : in STD_LOGIC;

start0 : out STD_LOGIC;

start1 : out STD_LOGIC;

yangsheng : in STD_LOGIC

);

End Component;

Signal NamedSignal_BELL1 : STD_LOGIC; -- ObjectKind=Net|PrimaryId=BELL1

Signal NamedSignal_BELL2 : STD_LOGIC; -- ObjectKind=Net|PrimaryId=BELL2

Signal NamedSignal_CLK : STD_LOGIC; -- ObjectKind=Net|PrimaryId=CLK

Signal NamedSignal_RST : STD_LOGIC; -- ObjectKind=Net|PrimaryId=RST

Signal NamedSignal_START1 : STD_LOGIC; -- ObjectKind=Net|PrimaryId=START1

Signal PinSignal_U1_bell : STD_LOGIC; -- ObjectKind=Net|PrimaryId=BELL1

Signal PinSignal_U1_light : STD_LOGIC_VECTOR(7 downto 0); -- ObjectKind=Net|PrimaryId=light

Signal PinSignal_U1_zb : STD_LOGIC_VECTOR(3 downto 0); -- ObjectKind=Net|PrimaryId=ZB[3..0]

Signal PinSignal_U2_jishi : STD_LOGIC; -- ObjectKind=Net|PrimaryId=jishi

Signal PinSignal_U2_start0 : STD_LOGIC; -- ObjectKind=Net|PrimaryId=START1

Signal PinSignal_U2_start1 : STD_LOGIC; -- ObjectKind=Net|PrimaryId=start1

Signal PinSignal_U3_TM : STD_LOGIC_VECTOR(7 downto 0); -- ObjectKind=Net|PrimaryId=TM[7..0]

Signal PinSignal_U3_yangsheng : STD_LOGIC; -- ObjectKind=Net|PrimaryId=yangsheng

Signal PinSignal_U4_fengmingqi : STD_LOGIC; -- ObjectKind=Net|PrimaryId=fengmingqi

Signal PinSignal_U5_bell : STD_LOGIC; -- ObjectKind=Net|PrimaryId=BELL2

Signal PinSignal_U6_FS1 : STD_LOGIC_VECTOR(7 downto 0); -- ObjectKind=Net|PrimaryId=FS1[7..0]

Signal PinSignal_U6_FS2 : STD_LOGIC_VECTOR(7 downto 0); -- ObjectKind=Net|PrimaryId=FS2[7..0]

Signal PinSignal_U7_fengmingqi : STD_LOGIC; -- ObjectKind=Net|PrimaryId=fengmingqi

begin

U7 : bjq

Port Map

(

baojing => BAOJING2,

bell => NamedSignal_BELL1,

fengmingqi => PinSignal_U7_fengmingqi

);

U6 : jfq

Port Map

(

add => ADD,

clk => CLK,

clr => CLR,

FS1 => PinSignal_U6_FS1,

FS2 => PinSignal_U6_FS2,

sub => SUB,

zubie => PinSignal_U1_zb

);

U5 : qdsc

Port Map

(

bell => PinSignal_U5_bell,

g0 => S0,

g1 => S1,

g2 => S2,

g3 => S3,

g4 => S4,

g5 => S5,

g6 => S6,

g7 => S7,

rst => NamedSignal_RST,

start => PinSignal_U2_start1

);

U4 : bjq

Port Map

(

baojing => BAOJING1,

bell => NamedSignal_BELL2,

fengmingqi => PinSignal_U4_fengmingqi

);

U3 : jsq

Port Map

(

clk => CLK,

jishi => PinSignal_U2_jishi,

rst => NamedSignal_RST,

stop => NamedSignal_BELL1,

TM => PinSignal_U3_TM,

yangsheng => PinSignal_U3_yangsheng

);

U2 : qiangda

Port Map

(

clk => NamedSignal_CLK,

en => EN_J1,

jishi => PinSignal_U2_jishi,

rst => RST_J0,

start0 => PinSignal_U2_start0,

start1 => PinSignal_U2_start1,

yangsheng => PinSignal_U3_yangsheng

);

U1 : qdsc

Port Map

(

bell => PinSignal_U1_bell,

g0 => S0,

g1 => S1,

g2 => S2,

g3 => S3,

g4 => S4,

g5 => S5,

g6 => S6,

g7 => S7,

light => PinSignal_U1_light,

rst => NamedSignal_RST,

start => NamedSignal_START1,

zb => PinSignal_U1_zb

);

继续——————————

-- Signal Assignments

---------------------

FENGMINGQI1 <= PinSignal_U4_fengmingqi; -- ObjectKind=Net|PrimaryId=fengmingqi

FENGMINGQI2 <= PinSignal_U7_fengmingqi; -- ObjectKind=Net|PrimaryId=fengmingqi

FS1 <= PinSignal_U6_FS1; -- ObjectKind=Net|PrimaryId=FS1[7..0]

FS2 <= PinSignal_U6_FS2; -- ObjectKind=Net|PrimaryId=FS2[7..0]

LED7_0 <= PinSignal_U1_light; -- ObjectKind=Net|PrimaryId=light

NamedSignal_BELL1 <= PinSignal_U1_bell; -- ObjectKind=Net|PrimaryId=BELL1

NamedSignal_BELL2 <= PinSignal_U5_bell; -- ObjectKind=Net|PrimaryId=BELL2

NamedSignal_CLK <= CLK; -- ObjectKind=Net|PrimaryId=CLK

NamedSignal_RST <= RST_J0; -- ObjectKind=Net|PrimaryId=RST

NamedSignal_START1 <= PinSignal_U2_start0; -- ObjectKind=Net|PrimaryId=START1

TM <= PinSignal_U3_TM; -- ObjectKind=Net|PrimaryId=TM[7..0]

ZB <= PinSignal_U1_zb; -- ObjectKind=Net|PrimaryId=ZB[3..0]

end structure;

------------------------------------------------------------

由上述生成的测试文件

------------------------------------------------------------

-- VHDL Testbench for fpga_project_xiugaiban

-- 2014 5 7 22 1 39

-- Created by "EditVHDL"

-- "Copyright (c) 2002 Altium Limited"

------------------------------------------------------------

Library IEEE;

Use IEEE.std_logic_1164.all;

Use IEEE.std_logic_textio.all;

Use STD.textio.all;

------------------------------------------------------------

------------------------------------------------------------

entity Testfpga_project_xiugaiban is

end Testfpga_project_xiugaiban;

------------------------------------------------------------

------------------------------------------------------------

architecture stimulus of Testfpga_project_xiugaiban is

file RESULTS: TEXT open WRITE_MODE is "results.txt";

procedure WRITE_RESULTS(

) is

variable l_out : line;

begin

write(l_out, now, right, 15);

writeline(RESULTS, l_out);

end procedure;

component fpga_project_xiugaiban

port (

);

end component;

begin

DUT:fpga_project_xiugaiban port map (

);

STIMULUS0:process

begin

-- insert stimulus here

wait;

end process;

WRITE_RESULTS(

);

end architecture;

------------------------------------------------------------

------------------------------------------------------------

呵呵 从来不用这个软件仿真 这个 电路不难 为什么不考虑直接用万能板搭呢

看一下编译时生成的messages 里面有相关的警告和错误